岁末年初,当我们回顾2014年产业界的发展时,少不了IoT(物联网)和Big Data(大数据)这两个2014年科技界人们谈论最多,捧的最高的科技名词。在IEEE公布的2014 TOP 10热搜排行榜上,他们也榜上有名。不过,拨开他们华丽的外衣,我们看到的是隐于其背后的各种先进的高性能及超低功耗半导体技术令人惊喜的发展。

功耗成为HPC和Networking的关键设计挑战

毫无疑问,IoT促进了低功耗的发展,但是,这只是问题的一个方面。另一方面,无所不在的移动设备产生了巨大的数据洪流,越来越多的远程监控系统以及嵌入式系统也产生了庞大的数据集,一些数据流只是在网络上流过而已。而有些会进行精细的分析,例如,从监控图像流中找出绑架了儿童的汽车牌照,或者每月才出现一次的希格斯玻色子等。大数据迫使我们大幅度提高网络和计算带宽。不过,在为数据中心加速的同时,功耗的问题就摆在眼前。

“大多数人们对于能耗受限的深切认识到来源于移动设备的电源续航能力的限制,这就给我们造成了一种错觉,以为只有移动设备是功耗敏感的应用,其实,在诸如数据中心等的高性能计算(HPC)及网络(Networking)领域,对于功耗的要求更加的苛刻。”富士通半导体市场部经理陈博宇(Alex Chen)先生在一年一度的中国集成电路设计业年会暨中国内地与香港集成电路产业协作发展高峰论坛(简称ICCAD峰会)上表示。

图1 富士通半导体市场部经理陈博宇先生在ICCAD上演讲

和手机固定功率的电源不同,数据中心的电源是永远开启的,整个机房的每个芯片无时无刻不在工作,对整个供电系统,包括散热系统的压力巨大。据统计:当服务器小于1万台,全年耗电约0.35亿千瓦时(电是次要因素);当服务器小于10万台,全年耗电约3.5亿千瓦时(电是重要因素);当服务器小于50万台,全年耗电约17.5亿千瓦时(电是主要成本);当服务器小于100万台,全年耗电约35亿千瓦时(电是TOP1成本)。

而和消费类的应用非常不同,在通信领域,对每个板卡的功耗都有要求,只有达到每块板卡的功耗要求,整个系统的功耗才能达标。“在高性能应用领域,亿门级的设计规模使得芯片的复杂度增加,如何在功耗上进行优化,而又能达到性能要求,这是在大规模设计上特别要考虑的。”陈博宇指出。

多种方法应对高性能设计的功耗挑战

现在的高速低功耗设计,最多有超过7亿多门级电路和超过2GHz的工作频率的设计。因此,设计人员需谨慎评估如何在最短的设计周期内,针对整个芯片的低功耗策略做定义及最佳化,并思考如何让封装设计满足超高的功耗。

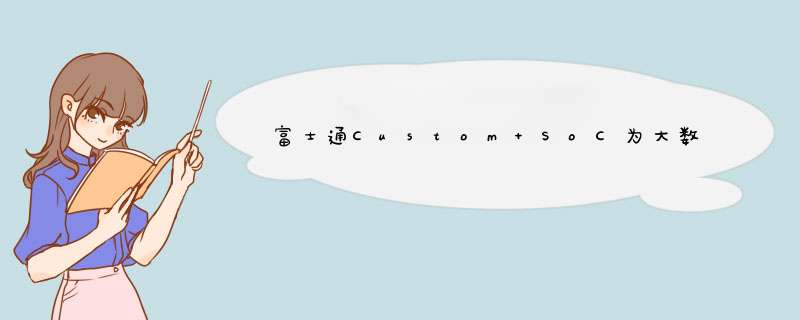

大规模版图设计能够帮助设计人员应对高速低功耗设计挑战,如下图所示2,富士通半导体的协同设计技术优化了芯片、IP、及从封装到板级设计等所有方面。为使其达到性能最优化,贯穿规划,设计,建模和分析所有过程,富士通半导体使用了可以预估的电源网络构架,并使用了层次化的电源网络分析,这种分析可以优化电源网络设计,并且最小化全芯片的功耗。低噪声的芯片架构设计可以承受超过300瓦的功耗。

图2 大规模版图设计能够帮助设计人员应对高速低功耗设计挑战

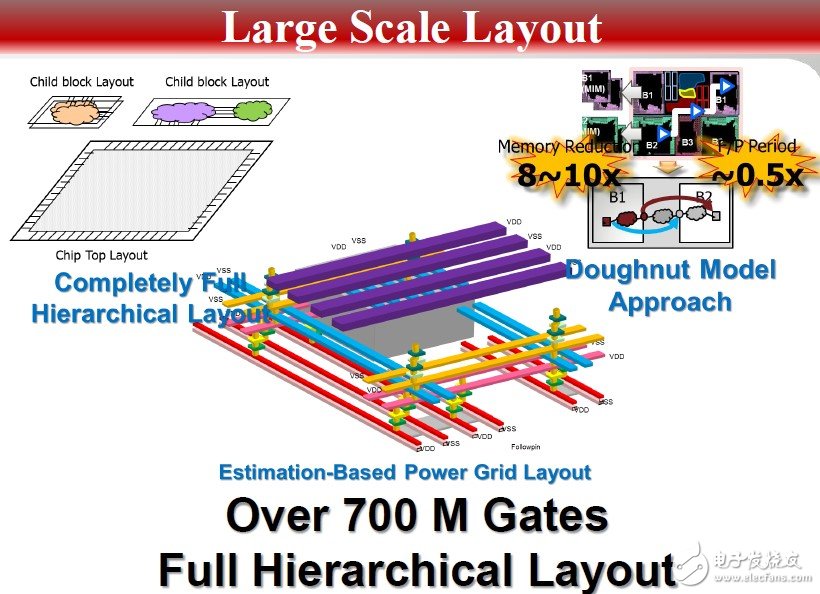

此外,特别值得一提的是富士通半导体独特的ASV(Adapter Support Voltage)技术。如下图3所示,该技术用以监控制程(process)的快慢。

图3 全功耗设计解决方案应对高速低功耗设计挑战

陈博宇进一步解释:“因为晶圆厂的制程存在快(fast)、慢(slow)、标准(typ)的状态,在芯片中放置‘Process Monitor’,使得我们可以读出制程的参数,这样就能知道电源的大小,例如,如果我们读出是偏快的制程,就可以帮助降低电压,因为功率是和电压的平方成正比,所以降低电压就能降低功耗,ASV技术就像一个d簧一样,把芯片拉向typ。”

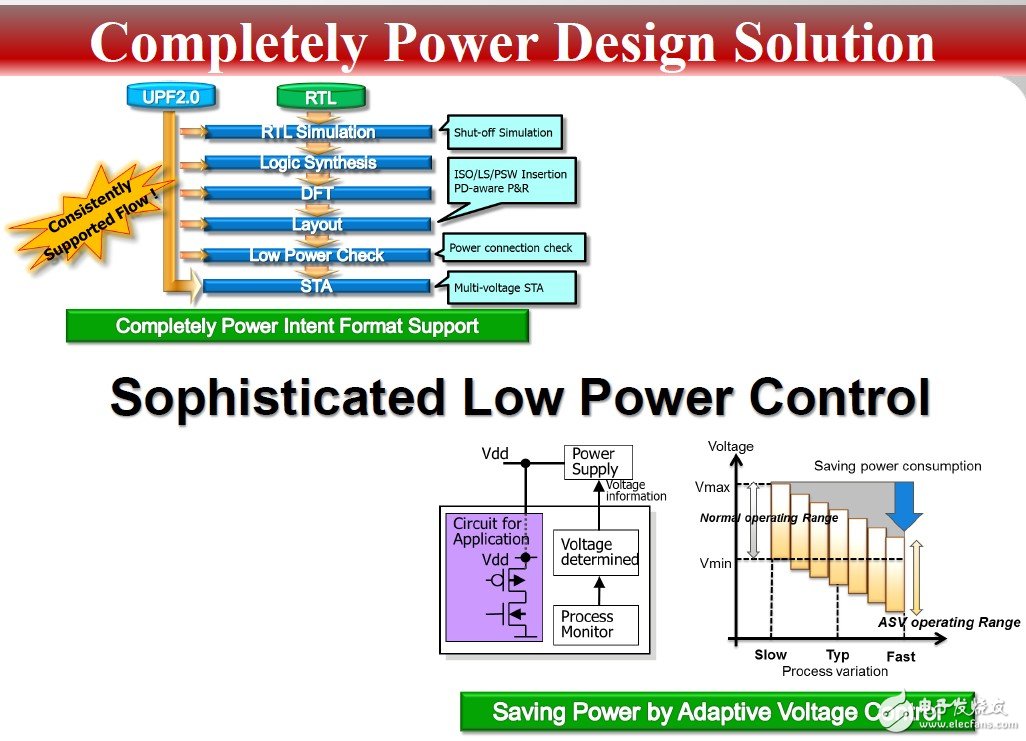

再次,高性能封装解决方案在应对功耗挑战上必不可少。富士通半导体在高性能封装市场也处于领先地位,在开发这些高可靠性封装的过程中,富士通半导体进行了严谨的模拟,优化了技术原型。如下图4所示。

图4 高性能封装解决方案应对高速低功耗设计挑战

“我们的球形封装技术支持到超过4000个pin脚,并且每一边的封装尺寸可以到达60mm,我们的多层基板封装设计可以支持到32层,对于BGA封装,我们独特的金属TIM实现了超低Theta JC,Theta JC小于0.05度,并通过了最新的热阻测量技术验证。我们正在为中央处理器和服务器,研制新一代2.5和3D封装技术。”陈博宇表示。

极具竞争的高速设计解决方案

随着芯片的处理速度不断提升,工作频率甚至超过2GHz,在高速设计中往往需要整合数亿颗同时运行的晶体管和超高速模拟互联IP,导致物理设计收敛变得更为困难,而芯片上大量的数字电路对超高速模拟IP的干扰现象也日益明显。

一方面,为实现高速设计富士通半导体使用了复杂的时钟分布技术,实现了低时钟偏差,并使用金属层隔离实现了无噪声设计,其先进的层次及缓冲器优化技术能够控制金属层的优化。

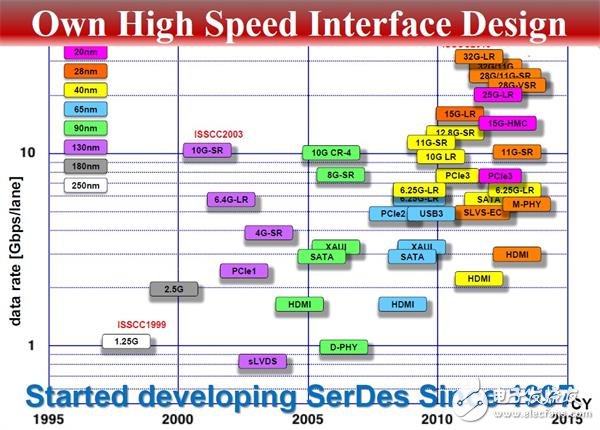

另一方面,自1999年富士通半导体研发出了超过1Gbps全球最快的SerDes以来,此后很多年,富士通半导体一直都是高速接口设计的领军者,满足了计算机网络设计,伺服器和消费电子的需求。现在富士通半导体的SerDes支持速率达到了32Gbps,并支持客户专用定制。针对最新32Gbps SerDes的评估板也以投入使用,未来还将支持56Gbps SerDes或更高参数。

如下图5所示,富士通半导体广泛的高速IP产品组合包括非常高速的SerDes,及PCIe和SATA等,这对于用户具有非常独特的价值,也是一般的IC设计服务公司所不具备的能力。“富士通半导体能够提供给客户整套的方案,我们宽泛的高速IP接口是经过验证的,用户采用我们的方案不会有IP验证方面的后顾之忧。”陈博宇表示。

图5 高速接口IP积累

50年磨一剑,在Custom SoC(ASICs)积累丰富Know-how

现在,富士通半导体拥有大规模版图经验,高速接口,高性能封装经验和协同设计能力,从设计到交付,始终支持客户的高性能LSI项目。

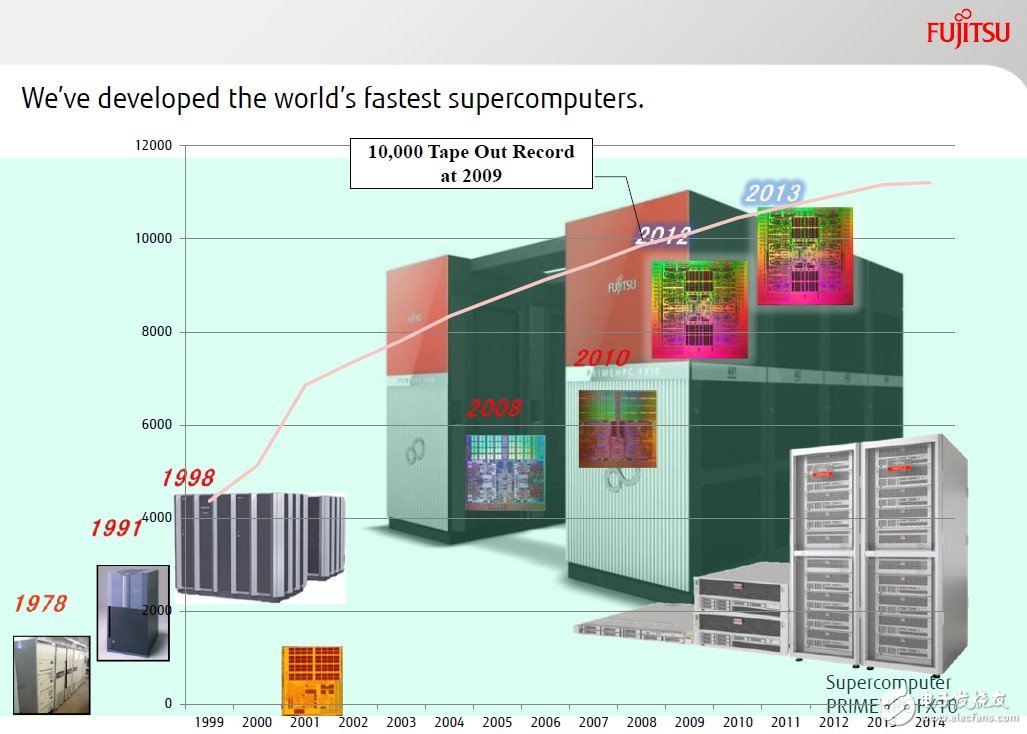

“从1956年出口了第一批硅晶体管开始,50年来,我们一直致力于对现有产品的不断提升并持续开发新产品。在CustomSoC(ASICs)领域积累了丰富Know-how。并且在HPC和Networking设计中,有很多成功的案例。2009年,我们的Tapeout总数达到10000个,每年的Tapeout数量都增加300多个。”陈博宇指出。

图6 2012年,富士通研发出了当时世界上最快的超级计算机

2012年,富士通半导体参与研发出了当时世界上最快的超级计算机“京”,“京”的计算速度为每秒1.051万万亿(1万万亿为1京)次。

据悉,富士通半导体与国内知名的网络芯片提供商在最近的一次高频通讯ASIC芯片的合作开发中,双方共同克服效能、功耗和交期的挑战,且原型芯片的Tapeout比原定计划提前两周,并一次成功。陈博宇进一步表示:“我们现在做的比较多的是在2亿到3亿门规模左右的设计,以28nm为主,预计接下来两年会有若干个16nm/14nm的2亿、3亿门级的设计。”

在现在充满竞争的市场中,面市时间常常决定了一种新产品的成功。借助我们多年的设计实践经验,富士通半导体先进的设计方法有助于保证我们的ASIC产品按计划推出并投入首次应用。凭借庞大的IP产品组合和全球设计团队的支持,富士通半导体将是您最佳的合作伙伴,可以帮助客户快速的将其创新理念转化为收益。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)