尽管 EEPROM 和闪存通常是大多数应用中非易失性存储器 (NVM) 的首选,但铁电 RAM (FRAM) 为能量收集应用中的许多低功耗设计提供了明显的优势,例如无线传感器节点、智能电表、和其他数据记录设计。凭借其延长的写入周期耐久性和数据保留时间,FRAM 技术可以帮助设计人员使用赛普拉斯半导体、富士通半导体、罗姆半导体等制造商提供的可用 FRAM IC 和基于 FRAM 的 MCU 满足长达十年的低功耗 NVM *** 作要求和德州仪器。

传统的 NVM,例如闪存和 EEPROM,以电荷载流子的形式将数据存储在浮栅中,这需要电荷泵将电压提升到迫使载流子通过栅极氧化物所需的水平。因此,加上这些设备固有的长写入延迟和高功耗,它们的高压写入 *** 作最终会磨损单元 - 有时只需 10,000 次写入周期。

FRAM 优势

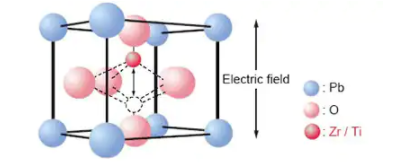

相比之下,铁电 RAM (FRAM) 通过铁电材料锆钛酸铅或 PZT (Pb (ZrTI)O 3 ) 的极化来存储数据,该材料作为薄膜放置在两个电极之间,类似于电容器的结构。 与 DRAM 一样,FRAM 阵列中的每个位都是单独读取和写入的,但 DRAM 使用晶体管和电容器来存储位,而 FRAM 使用由施加电场引起的相应位的晶体结构中的偶极位移穿过电极(图 1)。因为在电场移除后这种极化仍然存在,所以即使没有可用电源,FRAM 数据也会无限期地持续存在——这对于由不确定环境源供电的设计来说是一项至关重要的能力。

图 1:在 FRAM 单元中,数据存储为由在 PZT 薄膜上施加电场引起的极化状态 - 这种方法可以延长数据保留时间并消除浮栅技术中遇到的磨损。(富士通半导体提供)

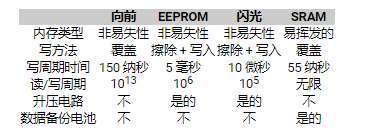

除了实现 FRAM 的非易失性外,晶体极化的使用还比基于电荷存储的技术具有许多优势(见表 1)。由于它避免了浮栅技术的潜在退化效应,FRAM 存储器的寿命及其在断电时保留数据的能力几乎是无限的。例如,富士通半导体MB85R1001A和 ROHM Semiconductor MR48V256A等 FRAM 存储器件都规定了 10 年的数据保留性能。

表 1:FRAM 与其他内存技术的比较。(富士通半导体提供)

通过消除对浮栅存储器技术所需的电荷泵的需求,FRAM 可以在 3.3 V 或更低的典型电源范围内工作。此外,与存储电荷存储设备不同,FRAM 设备对 α 粒子具有抵抗力,并且通常表现出低于可检测极限的软错误率 (SER)。

设计影响

FRAM 优势的影响会影响系统设计,例如无线传感器节点,这些系统需要结合高速写入和低功耗 *** 作。例如,凭借其高速率,设计人员可以使用单个 FRAM 器件,而他们可能需要多个并行排列的 EEPROM 器件来实现可接受的数据写入吞吐率。在那些 EEPROM 设计中,当一个 EEPROM 设备完成其写入周期时,控制器将按顺序在下一个 EEPROM 设备上启动写入 *** 作,依此类推。然而,使用 FRAM,所有写入都以随机访问的总线速度发生,没有基于内存的延迟或其他写入减慢。因此,与闪存相比,FRAM 存储器的写入速度通常要快得多,而且能耗要求要低得多。

设计人员还可以消除确保数据完整性所需的电源备份策略的需要。对于 EEPROM 系统,当检测到电源故障时,存储器控制器必须完成一个完整的写入周期以达到所需的数据块大小——需要额外的能量存储来确保基于 EEPROM 的设计中的写入周期完成。凭借其快速的循环时间,即使在突然断电的情况下,FRAM 也能够完成写入过程,从而确保数据完整性,而无需复杂的电源备份方法。

在应用层面,FRAM 的快速写入速度和低功耗运行还支持在无线传感器或电能表等能量收集应用中进行连续测量。在给定的功率预算下,与其他 NVM 技术相比,FRAM 设备将能够以更精细的粒度完成更多的读/写周期。

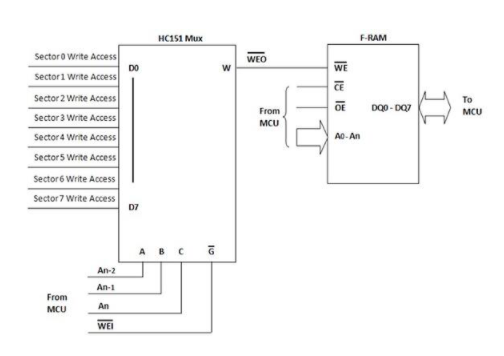

FRAM 还为开发人员提供了统一的内存架构,支持代码和数据的灵活分区,并允许更简单、更小的单芯片内存解决方案。同时,设计人员可以使用简单的写保护电路轻松保护存储在 FRAM 中的代码免受意外写入,从而为基于 FRAM 的设计提供可编程的块写保护功能(图 2,HC151 多路复用器)。

图 2:设计人员可以使用 HC151 等低功耗多路复用器来实现简单的与地址相关的写使能功能,以保护存储在 FRAM 器件中的代码。(由赛普拉斯半导体提供)

设备配置

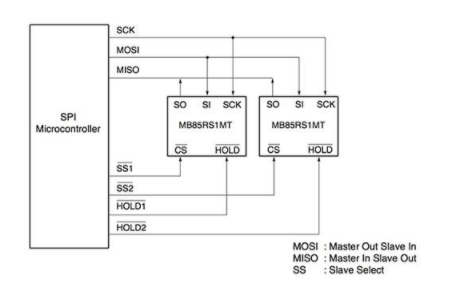

设计人员可以找到支持并行、SPI 串行或 I 2 C/2 线串行接口的 FRAM 存储器。例如,除了并行 1Mb MB85R1001A FRAM 外,Fujitsu 还提供 1Mb SPI 串行设备MB85RS1MT,使设计人员能够在典型的 SPI 主/从配置中使用任意数量的设备(图 3)。除了在比并行同类产品更低的电源电压下运行外,串行 FRAM 器件还为空间受限的设计提供更小的封装选项。例如,ROHM Semiconductor 的 32K SPI 串行MR45V032A采用 8 引脚塑料小外形封装 (SOP),宽度仅为 0.154“ 和 3.90 mm。

图 3:富士通 MB85RS1MT 等设备允许对配备 SPI 的 MCU 使用熟悉的主/从配置 - 或使用使用设备的 SI 和 SO 端口的简单总线连接解决方案进行非基于 SPI 的设计。(富士通半导体提供)

FRAM 技术的优势延伸到 MCU,例如带有片上 FRAM 的德州仪器 MSP430FR MCU 系列。在 MCU 中,FRAM 的高速 *** 作可加快整体处理速度,允许全速写入非易失性存储器,而不是强制 MCU 进入等待状态或阻塞中断。TI 的 FRAM MCU 系列从MSP430FR5739等器件扩展到其全功能MSP430FR5969系列。MSP430 系列中最小的器件,MSP430FR5739 采用 24 引脚 2 x 2 裸片大小的球栅阵列 (DSBGA),但还包括五个定时器、一个 12 通道 10 位 ADC 和直接存储器访问(DMA) 用于最大限度地缩短活动模式下的时间。

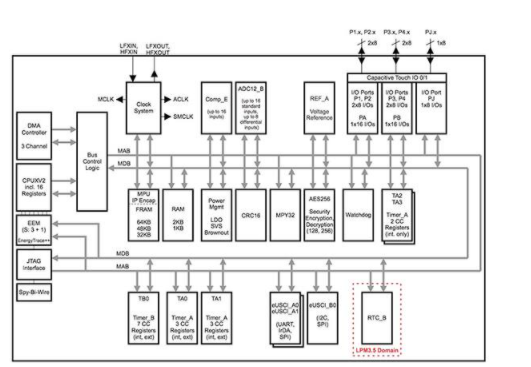

TI 的 MSP430FR5969 是该公司功耗最低的 MCU,具有大量片上 FRAM 存储(图 4)。在活动模式下,MCU 在启用实时时钟 (RTC) 的情况下仅需要 100 µA/MHz 的活动模式电流和 450 nA 的待机模式电流。该系列中的器件包括一套全面的外设和一个能够进行单输入或差分输入 *** 作的 16 通道 12 位模数转换器 (ADC)。这些 MCU 还具有 256 位高级加密标准 (AES) 加速和知识产权 (IP) 封装模块,用于保护关键数据。

图 4:Texas Instruments MSP430FR5969 MCU 将完整的外设与片上 FRAM 存储相结合,同时仅需要 100 µA/MHz 的活动模式电流,并且由于其多种低功耗模式 (LPM) 而显着降低。 (德州仪器提供)

结论

FRAM 设备提供具有 10 年数据保留时间的非易失性存储,而所需功率仅为熟悉的闪存和 EEPROM 替代品的一小部分。使用可用的基于 FRAM 的内存和 MCU 设备,工程师可以将这些强大的设备构建到低功耗能量收集应用程序中,并确信它们能够运行多年并在间歇性断电的情况下保持长期数据。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)