封装技术是一种将芯片与承载基板连接固定、引出管脚并将其塑封成整体功率器件或模块的工艺,主要起到电气连接、结构支持和保护、提供散热途径等作用[4]。封装作为模块集成的核心环节,封装材料、工艺和结构直接影响到功率模块的热、电和电磁干扰等特性。目前成熟的封装技术主要是以银胶或锡基钎料等连接材料、引线连接等封装结构为主,耐高温、耐高压性能差,电磁兼容问题突出,无法提供高效的散热途径。近来,烧结银互连材料、三维集成封装结构等由于具有优异的耐高温、高导热性能,可以实现双面散热、大幅降低开关损耗,使得功率模块具有良好的热、电特性和可靠性,获得了越来越多的研究和关注,有望满足第三代半导体器件在高温、高压和高频领域的可靠应用。本文针对功率电子封装结构设计的最新研究进展进行了总结和展望。

封装结构

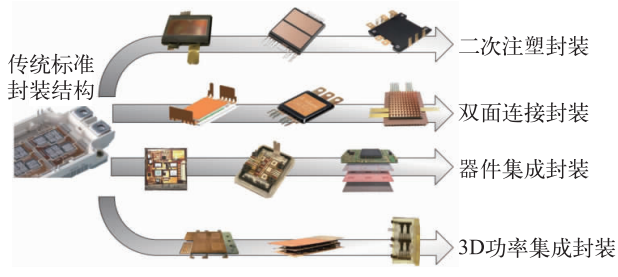

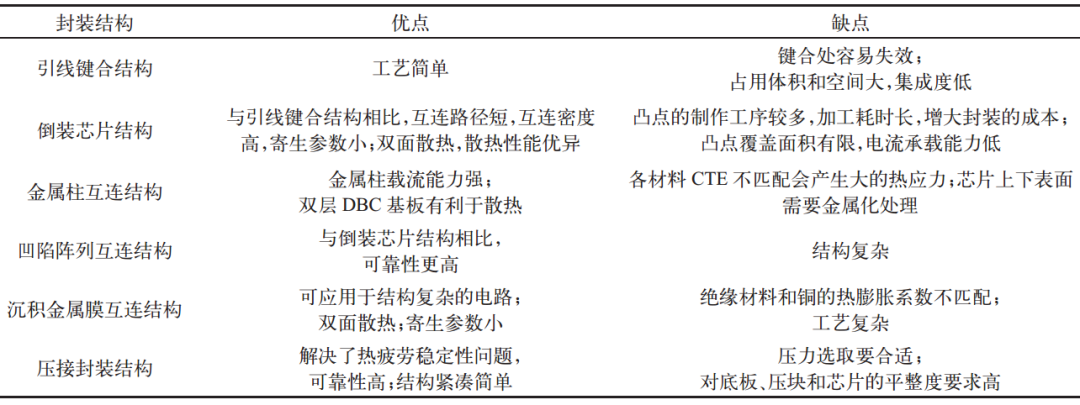

根据芯片组装方式和互连工艺的不同,功率电子封装结构可分为焊接式封装和压接式封装两种形式。封装结构的发展趋势如图4所示,其中焊接式封装可以采用引线键合、倒装芯片(BGA互连)、金属柱互连、凹陷阵列互连、沉积金属膜互连等结构。压接式封装是借助外界机械压力形成互连结构。为了便于对比分析,将上述几种封装方式的优缺点列于表6[18]。引线键合具有技术成熟、成本低、布线灵活等优点。然而,引线键合的模块具有较高的寄生电感,只能从底板单面散热[18]。并且,由于键合引线和芯片的CTE不匹配,产生较大的热-机械应力,使得焊点易疲劳失效,成为模块在功率循环过程中最主要的失效形式。

图4 封装结构的发展趋势[5]

表6 封装结构对比[18]

目前功率电子封装结构逐渐从传统的引线键合标准封装结构向二次注塑(Overmold)、双面连接(Double-Side Bonding)、器件集成(Component IntegraTIon)、三维功率集成封装结构(3D Power IntegraTIon)发展。通过去除引线,可以降低电磁干扰、提高散热效率、增大集成度。其中,注塑结构为紧凑型平面封装,易于批量模块生产;

双面连接结构可以实现双面散热,提高散热效率;器件集成结构可以将多种功能集成在模块内部,提高开关速度;三维功率集成结构是将芯片在垂直方向上堆叠连接,可大幅降低寄生电感,提升开关性能[5]。相比于二维封装,三维封装具有显著的优点,如可以在垂直方向上大大缩短回路距离,降低寄生电感和电磁干扰,提高传输速度,提高开关性能,降低功率损耗;可以集成多种芯片和器件,如门极驱动电路、去耦电容、散热器等,进一步提高功率集成密度,缩小封装体积。但是,三维封装目前也面临一些挑战,如芯片叠层互连带来的热管理、生产工艺和良率等问题,制程工艺有待进一步完善[6,19]。

3.1 二次注塑封装

二次注塑封装结构是在传统引线键合的封装结构基础上,将芯片直接粘接在引线框架上,去除了键合引线,并用环氧树脂进行注塑封装的结构。与引线键合的封装结构相比,注塑封装的芯片顶部连接面积增大,使得散热效率提高;寄生电感降低,使得功率损耗降低,并且非常利于模块化批量生产,在电动汽车的整流器中得到广泛应用。

3.2 双面连接封装

双面连接结构是将芯片分别与上、下基板连接,例如西门康公司提出的SKiN功率模块[20]、富士电机提出的铜针互连SiC功率模块[21]等,可以达到去除键合引线的目的。双面连接封装结构主要有两个优点:(1)消除发射极表面的引线键合,有效降低寄生电感,减小电压过冲和功率损耗,提高开关性能;(2)实现芯片上下两个方向散热,提高散热效率,有效降低芯片结温,从而减缓失效。美国橡树岭国家实验室提出了一种双面连接DBC基板封装的Si IGBT或SiC MOSFET功率模块,相比于传统的引线键合模块,其电感降低62%,开关损耗降低50%~90%,散热效率提高40%~50%[22]。

但双面连接结构也有一些缺点。第一,相比于引线键合模块,双面连接结构具有更多层材料,加大了封装工艺的复杂性。第二,各层材料的CTE不同,热失配会产生更大的热-机械应力,降低了连接层可靠性。为了降低热-机械应力,一些与芯片CTE匹配的金属,如Mo或Cu/Mo/Cu[23]等被用作中介层材料。第三,在实现不同厚度的多芯片双面连接的功率模块时,如图5所示,需要可以在芯片和DBC基板之间电镀或连接不同高度的微型金属柱(Micro-Metal Post)或铜顶针(Cu Pin)等,解决多芯片厚度不同带来的高度差异问题[6]。第四,锡基钎料是模块封装中最常用的互连材料,在双面连接模块封装过程中,通常需要多个连接步骤,这就需要一组具有不同熔点的钎料,限制了模块的服役温度。因此在双面连接封装结构中,具有高导热、高导电和高熔点的烧结银焊膏成为了互连材料的优先选择。

图5 双面连接封装结构[6]

3.3 器件集成封装

器件集成封装是在模块里集成多种功能的器件,例如集成门极驱动电路、去耦电容、温度传感器、电流传感器和保护电路等[18]。器件集成封装具有很多优点,例如通过集成门极驱动电路和去耦电容,可以降低母排或模块外部接插件的寄生电感,缩短功率器件和门极驱动之间的连接,降低门极回路电感,实现抑制电磁干扰,提高均流性能和开关速度。但是该封装结构也存在一定的局限性,例如,集成的门极驱动电路一般比较简单,模块的整体尺寸、载流能力和开关频率受各集成器件的限制。此外,在器件集成封装之前,需要检验各器件的耐温性能,避免因为器件集成距离太近,影响温度敏感器件的正常工作[5]。

3.4 三维功率集成封装

三维集成封装结构形式如图6所示,三维封装结构主要分为叠层型三维封装和埋置型三维封装[24],是在二维封装的基础上,采用引线键合、倒装芯片、微凸点、球珊阵列(Ball Grid Array,BGA)、硅通孔(Through Silicon Via,TSV)、PCB埋置等工艺技术,在垂直方向上实现多芯片的叠层互连[25-27]。

(a)叠层型封装:引线键合

(b)叠层型封装:BGA焊球连接

(c)叠层型封装:硅通孔连接

(d)叠层型封装:芯片堆叠连接

(e)叠层型封装:气相沉积晶圆连接

(f)埋置型封装:PCB埋置式连接图6 三维集成封装结构形式示意图[6,29-31]

在叠层型三维封装中,硅通孔是最受关注的技术之一,是利用穿透衬底的硅通孔的垂直互连,实现不同芯片之间的电气互连[28]。硅通孔封装关键技术包括硅通孔成形、填充、芯片减薄和互连等。具体步骤为:首先通过激光打孔、干法刻蚀或湿法刻蚀形成通孔,然后采用化学气相沉积等方法填充SiO2绝缘层和铜导电层,其次通过磨削加工减薄芯片,最后通过金属间键合或粘接等方法实现芯片互连[29]。与传统平面二维引线互连结构相比,硅通孔三维结构具有尺寸小、重量轻、硅片使用效率高、缩短信号延迟同时降低功耗等优点,被广泛应用于三维晶圆级、系统级和集成电路封装中。但它也存在一定的局限性,第一是可靠性,硅通孔封装结构的功率密度高,叠层芯片的热管理问题较大;第二是成本高,封装结构、工艺和测试复杂。

埋置型三维封装,是采用铜线和微孔代替键合引线,将芯片嵌入在PCB层压板中,可以缩小体积、提高可靠性,并且易于系统集成[30]。此结构面临最大的挑战是热-机械性能较差,受限于传统PCB材料的低玻璃转化温度和高CTE带来的热-机械应力,其服役温度较低[18]。此外,FR4-PCB层压板的剥离强度较低,约为0.9~1.25 N/mm,相比于DBC基板,PCB板嵌入式封装的模块可以承受的额定功率较低[3]。

除了上述焊接式连接之外,还可以通过压接形成三维封装,典型案例如图7所示,为西码(Westcode)IGBT压接模块内部结构图[32],各组件由外部施加的机械压力取代引线、钎焊或烧结形成物理连接,结构简单、成本较低、可靠性高,在高压大电流电网中得到了广泛应用。但是在压接模块中,对模块的内部尺寸、各组件的平整度和表面质量要求高,接头的导热和导电性能受压力大小和均匀性的影响很大,需要选择合适的合模压力来保证较小的接触电阻和接触热阻,但会不可避免地受到表面粗糙度和结构变形的影响。在压接结构中常引入CTE较小的d性缓冲结构和材料,如Mo或Be垫片、d簧片等,来均匀压力、降低热-机械应力,提高可靠性。

(a)示意图

(b)实物图

图7 西玛的IGBT压接模块内部结构[6,32]

结束语

功率电子封装的关键材料、连接技术和结构设计,逐渐向去除引线、提高散热性能、提高集成密度等方向发展,来满足高温、高压、高频环境的可靠应用。随着第三代半导体器件的推广应用,硅通孔技术、三维集成封装结构等是未来发展的主要趋势,相信其应用前景无限广阔。

审核编辑:汤梓红

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)