前言

在做射频链路电路仿真时,除了需要搭建原理图的器件模型电路,设计者还需要考虑到实际版图结构中传输线、过孔所带来的阻抗不连续性和串扰,以及介质材料的损耗特性带来的影响。因此,在前期建模过程中需要加入版图的结构,来模拟实际版图结构和材料的真实特性。

芯和半导体XDS平台不仅能够支持射频电路的电磁场仿真,也允许用户在该平台下完成基本版图结构的手动绘制,利用其2D版图编辑功能,方便用户进行前期版图设计和优化的预研工作。

射频PCB版图绘制流程

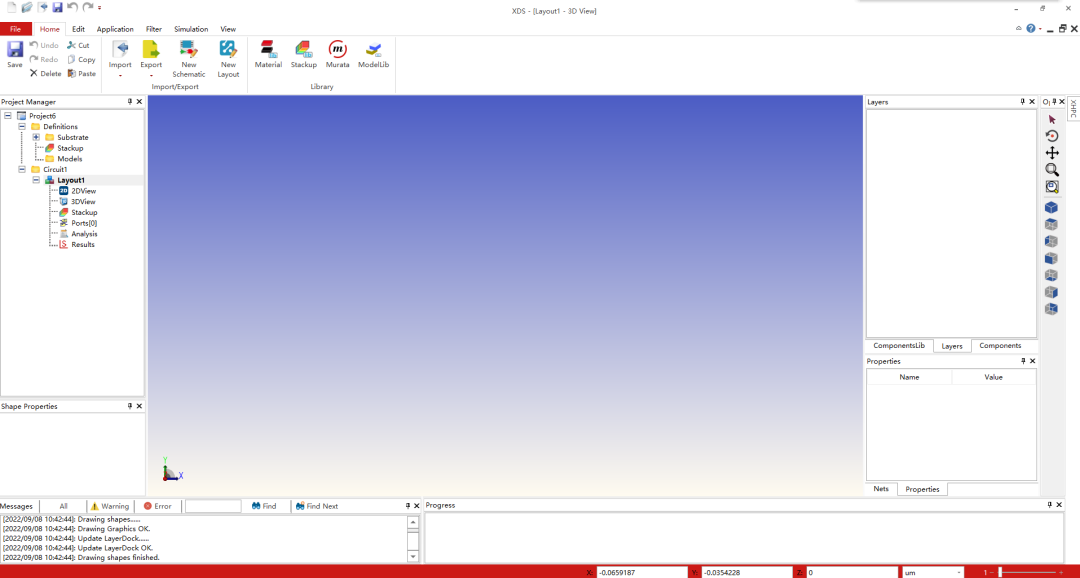

1. 创建layout绘制区域

XDS集成了原理图和版图两大功能模块。首先,进入到XDS主界面,点击New Layout,创建一个空白的layout模型,用户除了可以通过导入常见设计文件(.brd/ .sip/ .mcm/ ODB++/ .gds)的方式创建版图模型外,还可以在此区域中手动绘制PCB版图。

图1. 创建layout

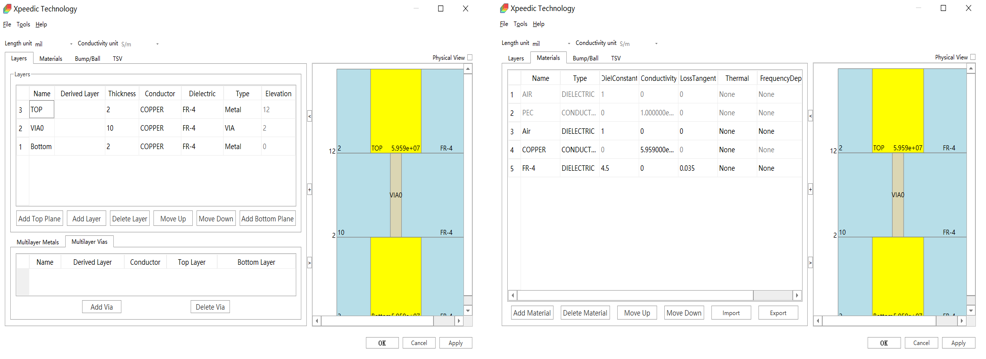

2. 创建叠层文件

点击layout模型工程树下的Stackup,进入到叠层编辑的页面,如图2所示。在此页面Layers栏中设置每层的名字和厚度以及所赋予的材料,Materials栏中编辑所用到的材料参数。在本案例中,创建了两层的叠层,Top层作为信号走线层,Bottom为参考平面层,中间通过Via层互连。

图2. 叠层文件设置

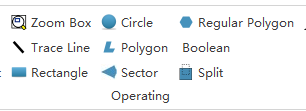

3. 绘制版图图形

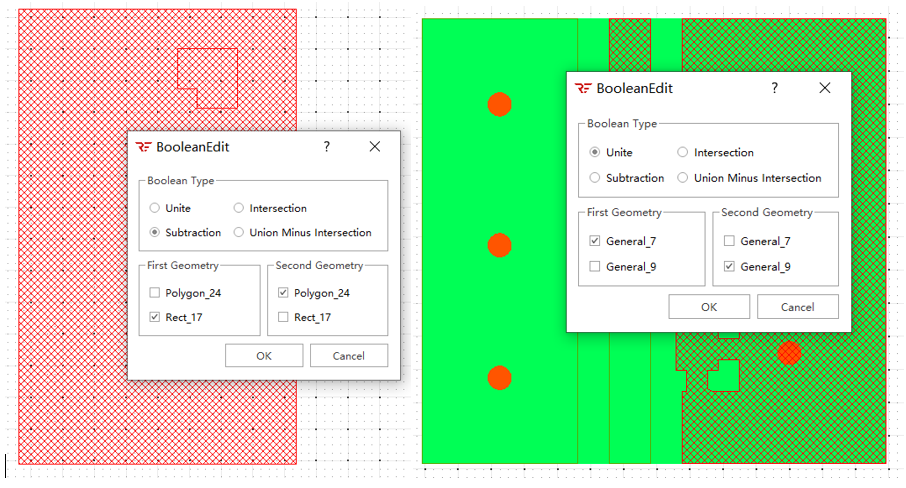

进入到2D view视图中,在Edit菜单栏下,有多种常用的图形可供用户选择,包含Rectangle、Circle、Polygon、Sector、Polygon等,用户可根据设计需要选择不同的形状,也可以进行不同图形之间的布尔运算,例如合并、相减等常见 *** 作,如图3所示。

图3. 选择绘制的图形

若要在某一层绘制图形,只需要在Layer窗口中选择所要绘制的层,使当前层在选中状态,就可以在本层中绘制所需的图形了。例如图4中,可以对矩形和多边形进行布尔运算;同理,分别完成Top层、Via层、Bottom层相应版图的绘制。

图4. 不同图形的布尔运算

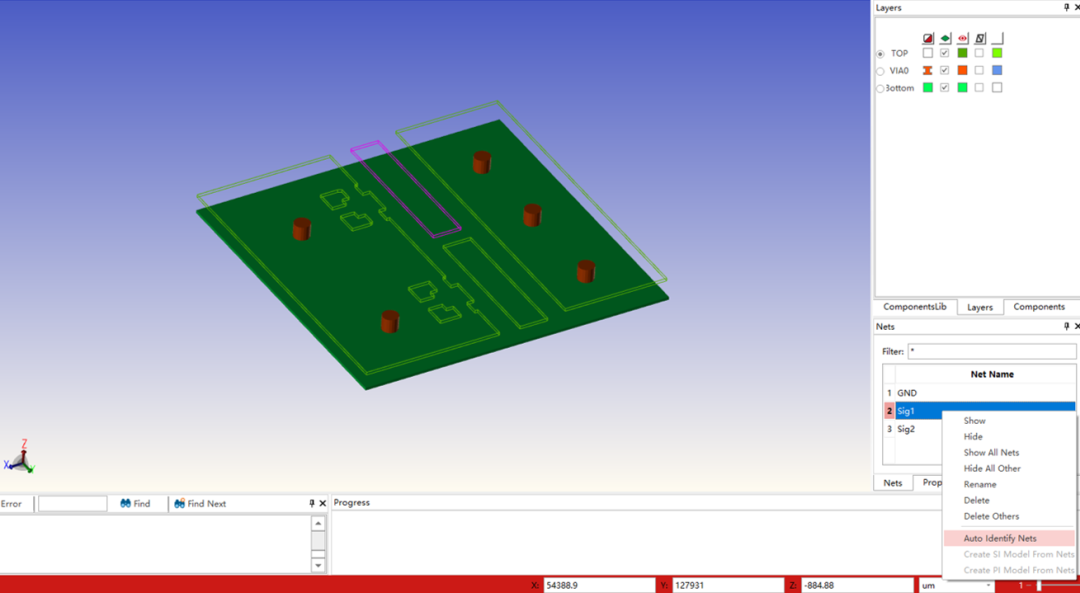

4.Net定义

完成版图的绘制后,进入到3D View试图,可分层检查所绘制的图形是否正确,并在Nets窗口右键点击Auto IdenTIfy Nets,可对整个版图的网络进行重构,如图5所示。

图5. 重构网络

5. 仿真设置

在版图相应的位置添加仿真端口,添加好的Port会出现在工程树中的Ports列表中,本案例将生成好的版图symbol拖拽到原理图界面,添加好器件模型,如图6所示。

图6. 原理图

6.运行仿真,结果展示

添加Frequency Domain Analysis仿真项,设置好仿真的扫频频率,右键点击Analyze,就可以进行仿真。待Message窗口出现Analysis Successfully提示,表示仿真已完成,XDS内置强大的S参数后处理模块,可以在Results下查看仿真结果。

图7. 仿真结果

总结

本文介绍了采用芯和半导体XDS软件中的2D 编辑功能实现手动绘制layout的流程,此功能中包含了常用的矩形、圆形、扇形、多边形等基本图形,并支持多图形之间的布尔运算,可满足用户日常对PCB版图中走线、过孔、焊盘、地平面等结构的绘制,灵活实现版图的自由编辑。

审核编辑:汤梓红

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)