3D集成电路技术的发展始于多年前,远早于摩尔定律效益放缓成为讨论话题之前。该技术最初用于堆叠功能块,功能块之间具有高带宽总线。内存厂商和其他IDM在早期通常会利用这项技术。由于该技术本身并不局限于此类用途,因此该技术一直具有更广泛的吸引力和潜力。

多年来,3D IC技术已从初始阶段发展成为一种成熟的主流制造技术。EDA行业引入了许多工具和技术来帮助设计采用3D IC路径的产品。最近,复杂的SoC实现开始利用3D IC技术来平衡性能和成本目标。

摩尔定律的放缓已成为实现SOC的小芯片方式的主要驱动因素。小芯片是专为与其他小芯片和全尺寸集成电路一起在封装内运行而设计和优化的小型集成电路。越来越多的公司转向在不同工艺节点中实现的集成电路和小芯片的3D堆叠,以优化各自的小芯片功能。设计者还可以在同一封装内的硅内插层上组合3D存储器堆栈,例如高带宽存储器。3D IC实现将是小芯片采用浪潮的主要受益者。

当一项新功能准备好成为主流时,其大规模采用的成功取决于解决方案交付的容易、快速、有效和高效程度。虽然3D IC制造技术可能已成为主流,但成功实现异构3D IC仍有一些基础支持因素。西门子EDA最近出版了一本关于这一主题的电子书,作者是Keith Felton。

这篇文章将重点介绍电子书中的一些要点。后续文章将介绍在实施3D IC设计时实现最佳结果的方法和工作流程建议。

成功实现异构3D IC的基础推动力

任何好的设计方法总是包括对下游效应的前瞻性,以便在设计过程的早期考虑和解决它们。虽然这对于单片设计也很重要,但在设计3D IC时变得至关重要。

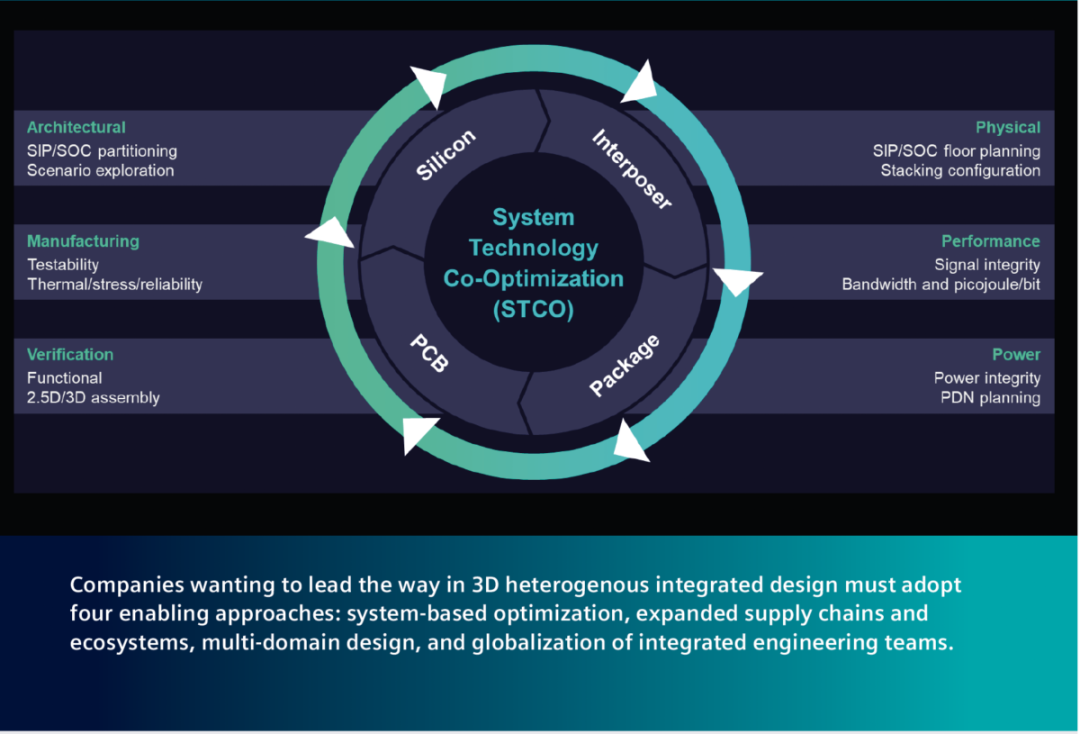

系统协同优化(STCO)方法

这种方法涉及从架构级别开始,根据功能需求和形状因子约束将系统划分为各种小芯片和封装裸片。在此步骤之后,生成RTL或功能模型。随后是物理楼层规划和验证,一直到过程性能建模支持的详细布局。

STCO元素已经存在于许多西门子EDA工具中,使工程师能够在可布线性、功率、热和可制造性的预测下游影响的背景下评估设计决策。预测建模是STCO方法的基本组成部分,该方法在物理规划期间利用西门子EDA建模工具,以尽早了解下游性能。

从基于设计到基于系统的优化过渡

3D IC 设计需要在整个设计和集成过程中保持一致的系统表示,并具有所有跨域内容的可见性和互 *** 作性。这需要能够从早期规划到实施再到设计验收和制造交接的完整系统视角的工具和方法。

扩大供应链和工具生态系统

3D IC设计工作需要比业界更高水平的工具互 *** 作性和开放性。必须支持在多供应商或多工具环境中共享和更新设计内容。这对整个设计过程中的装配级验证提出了更高的要求,以确保系统的不同部分按预期一起工作。

跨多个领域平衡设计资源

STCO有助于探索3D IC解决方案空间,实现所有领域资源的理想平衡,并得出最佳产品配置。早期的视角能够更好地进行资源分配的工程决策,从而产生性能更高、成本效益更高的产品。

更紧密地整合各个团队

需要新的设计流程来支持3D IC设计中多个ASIC、小芯片、存储器和插入器的设计、验证和集成。芯片、封装和PCB团队更可能是全球性的,需要与系统、RTL和ASIC设计流程进行更紧密的集成。

有关西门子EDA 3D IC创新的更多详细信息,请下载西门子EDA出版的电子书。

虽然西门子异构3D IC解决方案具有强大的功能,但能否充分利用这些功能取决于所采用的实施方法。设计具有差异化、盈利能力和上市时间优势的3D IC产品后续将继续讨论。

编辑:黄飞

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)