在设计ADC电路时,一个常见的问题是“如何在过压条件下保护 ADC输入”,那么....

在过压情形中可能出现哪些问题呢?

发生的频率又是怎样的呢?

有木有潜在的补救措施呢?

针对上述问题,让我们进行一次深入分析吧!

ADC输入的过驱一般发生于驱动放大器电轨远远大于ADC最大输入范围时,例如,放大器采用±15 V供电,而ADC输入为0至5V。高压电轨用于接受±10 V输入,同时给ADC前端信号调理/驱动级供电,这在工业设计中很常见,PLC模块就是这种情况。如果在驱动放大器电轨上发生故障状况,则可因超过最大额定值而损坏ADC,或在多ADC系统中干扰同步/后续转换。

这里讨论的重点虽然是如何保护精密SAR ADC,如AD798x系列,但是,这些保护措施同样适用于其他ADC类型哦~

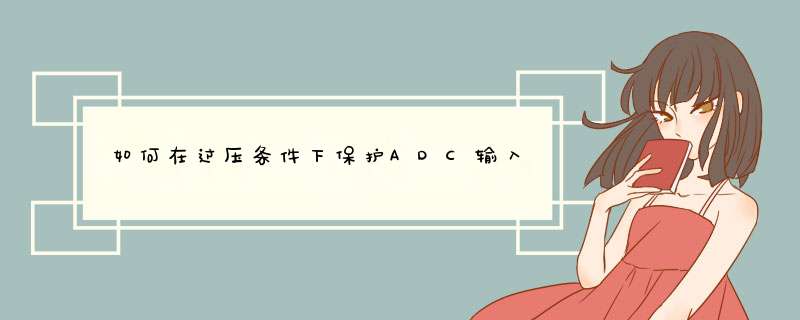

试考虑图1中的情形。

图1. 精密ADC设计的典型电路图

上图电路代表AD798X(例如AD7980)系列PulSAR ADC中的情形。输入端、基准电压源和接地之间存在保护二极管。这些二极管能够处理最高130mA的大电流,但仅能持续数毫秒,不适用于较长时间或重复过压。在一些产品上,例如AD768X/AD769x(如AD7685、AD7691)系列器件,保护二极管连接至VDD引脚而不是REF。在这些器件上,VDD电压始终大于或等于REF。一般而言,此配置更有效,因为VDD是更稳定的箝位电轨,对干扰不敏感。

图1中,如果放大器趋向+15 V电轨,则连接至REF的保护二极管将开启,放大器将尝试上拉REF节点。如果REF节点未通过强驱动器电路驱动,则REF节点(及输入)的电压将升至绝对最大额定电压以上,一旦电压在该过程中超过器件的击穿电压,ADC可能受损。图3举例说明了ADC驱动器趋向8 V而使基准电压(5 V)过驱的情况。许多精密基准电压源无灌电流能力,这在此情形中会造成问题。或者,基准驱动电路非常强劲,足以将基准电压保持在标称值附近,但仍将偏离精确值。

在共用一个基准电压源的同步采样多ADC系统中,其他ADC上的转换不精确,因为该系统依赖于高度精确的基准电压。如果故障状况恢复时间较长,后续转换也可能不精确。

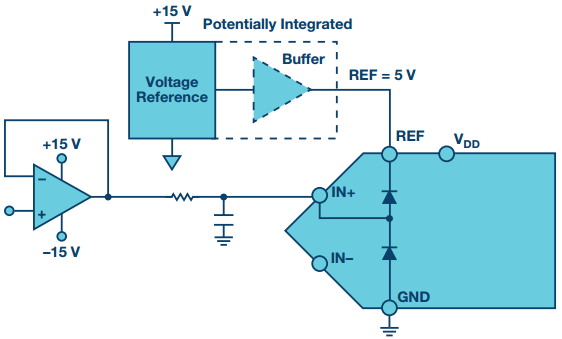

缓解此问题有几种不同方法。最常见的是使用肖特基二极管(BAT54系列),将放大器输出钳位在ADC范围。相关说明详见图2和图3。如果适合应用需求,也可使用二极管将输入箝位在放大器。

图2. 精密ADC设计的典型电路图

(添加了肖特基二极管和齐纳二极管保护)

在此情况中,之所以选择肖特基二极管,是因为其具有低正向导通压降,可在ADC内的内部保护二极管之前开启。如果内部二极管部分开启,肖特基二极管后的串联电阻也有助于将电流限制在ADC内。对于额外保护,如果基准电压源没有/几乎没有灌电流能力,则可在基准节点上采用齐纳二极管或箝位电路,以保证基准电压不被过度拉高。在图2中,为5V基准电压源使用了5.6V齐纳二极管。

图3. 黄色 = ADC输入,

紫色 = 基准电压源。

左侧图像未添加肖特基二极管,

右侧图像添加了肖特基二极管

图4. 黄色 = ADC输入,

绿色 = ADC驱动器输入,

紫色 = 基准电压源(交流耦合)

左侧图像未添加肖特基二极管,

右侧图像添加了肖特基二极管(BAT54S)

图4中的示例显示了以正弦波使ADC输入过驱时,给ADC输入添加肖特基二极管后对基准输入(5 V)的影响。肖特基二极管接地,5 V系统电轨能够吸电流。如果没有肖特基二极管,当输入超过基准电压和地电压一个压降时,就会出现基准电压源干扰。从图中可看到,肖特基二极管完全消除了基准电压源干扰。

需要注意肖特基二极管的反向漏电流,此电流在正常运行期间可引入失真和非线性。该反向漏电流受温度影响很大,一般在二极管数据手册中指定。BAT54系列肖特基二极管是不错的选择(25°C时最大值为2μA,125°C时约100μA)。

完全消除过压问题的一种方式是为放大器使用单电源电轨。这意味着,只要为基准电压(最大输入电压)使用相同电源电平(本例中为5V),驱动放大器就绝不会摆动至地电压以下或最大输入电压以上。如果基准电路具有足够的输出电流和驱动强度,则可直接用来为放大器供电。图5中显示了另一种可能性,也就是使用略低的基准电压值(例如,使用5 V电轨时为4.096 V),从而显著降低电压过驱能力。

图5. 单电源精密ADV设计的典型电路图

这些方法可解决输入过驱的问题,但代价是ADC的输入摆幅和范围受限,因为放大器存在上裕量和下裕量要求。通常,轨到轨输出放大器可在电轨十几mV内,但也必须考虑输入裕量要求,可能为1 V或更高,这会将摆幅进一步限制在缓冲器和单位增益配置内。该方法提供了最简单的解决方案,因为不需要额外保护元件,但依赖正确的电源电压,可能还需要轨到轨输入/输出(RRIO)放大器。

放大器与ADC输入之间的RC滤波器中的串联R也可用于在过压状况期间限制ADC输入处的电流。不过,使用此方法时需要在限流能力与ADC性能做出取舍。较大的串联R提供较佳的输入保护,但会导致ADC性能出现较大失真。如果输入信号带宽较低,或者ADC不在满吞吐速率下运行,这种取舍可行,因为此情况下串联R可以接受。应用可接受的R大小可通过实验方式确定。

如上文所述,保护ADC输入没有成法,但根据应用要求,可采用不同的单独或组合方法,以相应的性能取舍提供所需的保护水平。

审核编辑:汤梓红

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)