图1

1、 指令控制器

指令控制器是控制器中相当重要的部分,它要完成取指令、分析指令等 *** 作,然后交给执行单元(ALU或FPU)来执行,同时还要形成 下一条指令的地址。

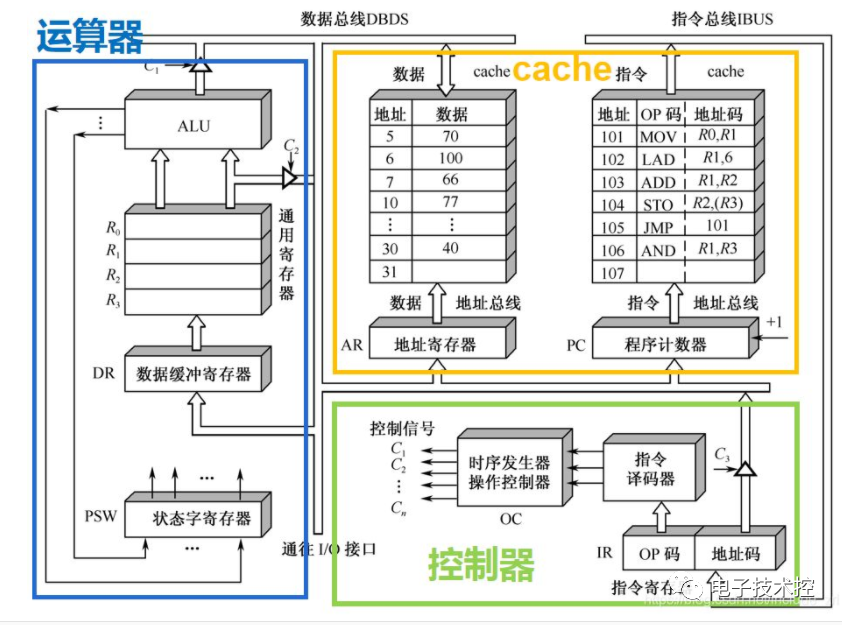

为了说明这个问题,这里转载一个指令执行示意图。

图2

从上图可以看到,由CS:IP构成的寄存器总是给出当前要执行的指令地址,并在当前指令尚未执行完成的时候,给出下一条将要执行的指令地址。CS:IP就是图1中的PC指针。这是控制器的最主要作用。

2、 时序控制器

时序控制器的作用是为每条指令按时间顺序提供控制信号。时序 控制器包括时钟发生器和倍频定义单元,其中时钟发生器由石英晶 体振荡器发出非常稳定的脉冲信号,就是CPU的主频;而倍频定义单元则定义了 CPU主频是存储器频率(总线频率)的几倍。

图3

假设现在要执行一条指令:MOV A, data1,这条指令的意思很简单,就是通过CPU找到内存中的某个数据data1,然后把它放到寄存器A里面。这条指令执行完应该分为以下几步:

第一步:找到这个数据在内存中的位置(地址号)。

第二步:保证这个数据可以被CPU读出(未被锁定)。

第三步:把这个数据读出来,并存入寄存器A中。

上面三步的时间顺序不能乱,否则指令执行肯定会出错。从图3可以看出,地址信号首先有效,然后是读信号有效,最后才是被读的数据出现在数据线上面。

这和我们实际生活中的这个例子非常类似,假设服务员要到宾馆的某个房间登记里面客人的身份信息,同样分为三步:

第一步:找到这个客人的位置(房间号)。

第二步:客人打开房门。

第三步:登记客人信息。

3、 总线控制器

总线控制器主要用于控制CPU的内外部总线,包括地址总线、数 据总线、控制总线等等。

图4

图5

计算机内部的主要工作过程是信息传送和加工的过程,为了便于对总线进行管理,组成了总线结构,使不同来源的信息分时在总线上传送。

从图4图5可以看到,总线的使用同样受到时序控制部件的控制。总线控制同样可以从图3得到很好的理解:当把数据从存储单元读出以前,地址信号必须保持有效。

从上图可以看到,一条指令何时占用总线,要由专门的时钟脉冲产生的时钟信号决定。

计算机还有一个DMA结构,当进行DMA *** 作时,cpu可以让出自己对总线的控制权。

也就是说,总线上什么时候有何种信号,什么时候没有,信号持续时间多长,甚至cpu的总线控制权都可以出让,这些都属于总线控制的内容。

中断控制器用于控制各种各样的中断请求,并根据优先级的高低 对中断请求进行排队,逐个交给CPU处理。

上图中有多个中断源,这些中断有可能同时产生中断请求,为了对这种情况进行管理,每个中断源都被赋予了一个优先级,以保证某个时刻只有一个中断可以得到响应。中断控制器有的在cpu芯片外部,比如8259A中断控制器,也有集成在cpu芯片内部的,

例如ARM 的Cortex系列。

按照上面的叙述,计算机控制器的功能主要包括:

指令控制、时序控制、总线控制和中断控制等。

审核编辑:汤梓红

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)