0 引言

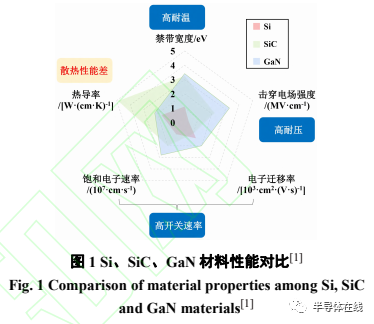

近年来,电动汽车、高铁和航空航天领域不断发展,对功率器件/模块在高频、高温和高压下工作的需求不断增加。传统的 Si 基功率器件/模块达到其自身的材料性能极限,氮化镓(GaN)作为第三代宽禁带半导体材料具有高耐温、高耐压及高开关速率的优点逐渐成为研究热点。图 1所示是三代半导体材料性能对比图。然而封装技术为充分发挥 GaN 的材料优势带来了挑战。

首先,GaN 器件的开关速度极高,如果使用传统引线键合封装型式会带来较大的封装杂散电感,继而产生显著的开关损耗、电压过冲等问题。这无法满足 GaN 器件的高频应用需求。为此,国内如北京工业大学(Beijing University of Technology, China),国外如韩国电子通信研究院 (Electronic Technology Research InsTItute, Korean)、美国弗吉尼亚理工大学(Virginia Tech, USA)等高校和研究机构相继提出了调整引线级联的方式降低杂散电感的研究思路,但效果有限。随后为进一步解决这一突出难题,美国弗吉尼亚理工大学、德国埃尔朗根-纽约堡大学(Erlangen Nurnberg University, German)和韩国汉阳大学(Hanyang University, Korean)等相继提出了二维平面型无引线封装型式。为进一步缩短电流环路面积,德国弗劳恩霍夫可靠性与微集成研 究 所 (Fraunhofer InsTItute for Reliability and MicrointegraTIon IZM, German)、美国东哈特福德联合技术研究中心(Systems Department United Technologies Research Center East Hartford, USA)、 丹 麦 奥 尔 堡 大 学 (Aalborg University, Denmark)和美国弗吉尼亚理工大学等进一步探索了三维集成型无引线封装型式。此外,美国弗 吉尼亚 理工大 学 、美 国 EPC(Efficient Power Conversion)公司、韩国汉阳大学等公司和高校基于磁相消设计的理念提出降低杂散电感的优化方案。

其次,随着 GaN 功率器件/模块朝着高功率密度化、高集成化方向发展,其热流密度越来越大。而且加之 GaN 材料本身热导率低,由此引发的封装引线热烧损和 GaN 芯片热击穿等问题突出。因此,GaN 功率器件/模块封装需要具备快速、高效散热能力。欲加入三代半交流群,加微信:tuoke08。国内如西安交通大学(Xi’an Jiaotong University, China),国外如法国巴 黎 第 十 一 大 学 (University Paris-Sud, France)、 美 国 威 斯 康 星 大 学 麦 迪 逊 分 校(University of Wisconsin-Madison, USA)、德国英飞凌公司(Infineon, German)等高校和公司分别对传统远结被动冷却封装形式改进设计优化GaN 功率器件/模块的散热,但是依然不能满足其更高热流密度的工作需求。为此,美国休斯研究室(Hughes Research Laboratories, USA)和德国弗劳恩霍夫可靠性与微集成研究所相继提出以扇出式晶圆级封装结构为主的近结被动冷却封装形式,已经引起广泛的关注。此外,日本松下电气公司(Panasonic, Japan)和美国洛克希德·马丁任务系统与训练分公司(Lockheed MarTIn Mission System and Training, USA)还提出将散热系统与 GaN 功率器件集成的改良型近结主动冷却封装形式,散热效率大幅提升。

最后,芯片封装互连材料是保证 GaN 功率器件/模块高温下可靠使用的关键。然而功率器件/模块中常用的钎料合金在高温工作条件下存在抗蠕变疲劳性能和抗机械疲劳性能差等问题。为了解决这些问题,德国弗莱堡大学(UniversityFreiburg, German)讲锡银合金的瞬时液相连接应用在 GaN 芯片封装中,并获得高连接质量的接头,但是工艺复杂,成本高。近年来,低温烧结银互连由于具有低烧结工艺温度、高允许工作温度的优势而被广泛关注。日本大阪大学(Osaka University, Japan)将烧结银作为连接材料,应用在 GaN 芯片的封装中,并分别针对芯片连接层结构和基板表面镀层做了相关研究。

综上,本文以 GaN 芯片的封装技术为核心,基于现有文献资料,总结分析 GaN 功率器件/模块在杂散电感、散热设计以及可靠性方面遇到的问题及解决方案,同时分析并指出未来GaN 功率器件/模块封装技术的热点研究方向。期望通过提出该领域亟待解决的问题以及研究展望,为今后研究提供思路。

1 GaN 基功率器件/模块封装需求

虽然 GaN 基功率器件/模块的封装研究刚起步,但 Si 基、SiC 基功率器件/模块的封装研究趋于成熟。三者之间存在显著差异,亦有相互借鉴之处。

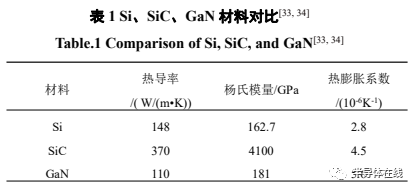

首先在减小封装杂散电感方面,SiC 和 GaN基功率器件/模块相比于 Si 基,其开关速度更快,同时伴随着更高的 dv/dt 和 di/dt。此外,两者的开关频率也更高。因此,SiC 和 GaN 更易产生电压过冲和电磁干扰等问题。以 GaN 器件为例,其 dv/dt 一般可以超过 100V/ns。例如,2016 年,美国弗吉尼亚理工大学制作的无引线封装 Cascode GaN HEMT 器件具有极高的开关速度,关断时的 dv/dt 和 di/dt 分别可达 100V/ns和 3A/ns。由于该器件是分立 GaN 器件,其开关速度依然有提升的潜力。2021 年,美国纽约州立大学石溪分校(The State University of NewYork at Stony Brook, USA)将栅极驱动集成到模块中去,缩短驱动环路和功率环路,进一步提高开关速度。该成果是目前开关速度最快的 GaN功率模块:关断时间小于 15ns,关断时 dv/dt 达192V/ns,电压过冲仅为 58V,低于直流母线电压的 15%。引线键合封装型式虽然可以满足 Si基器件/模块的使用要求,但不能满足 SiC 基和GaN 基器件/模块。而且,在 Cascode GaNHEMT 中,由于涉及到 GaN HEMT 与 MOSFET的级联,杂散电感会更大。因此,GaN 基功率器件/模块对低杂散电感封装需求更加迫切。其次在封装散热管理方面,GaN 材料热导率在三者之中最低,而且同功率等级下 GaN 器件的面积往往更小。虽然当前 GaN 功率器件/模块的功率等级低于 SiC 基功率器件/模块,但为降低封装杂散电感,GaN 功率器件/模块通常要求将其驱动电路部分甚至完全与 GaN 功率器件/模块一体化集成,并且随着 GaN 功率器件/模块不断发展,功率等级不断提升,因此其热流密度非常高。而且加之目前 GaN 芯片多为平面型结构,其散热形式主要为单面散热,散热效率低,当前封装无法满足高热流密度下快速、高效的散热要求。因此,不难看出 GaN 功率器件/模块对快速、高效封装散热技术的需求甚至要高于 SiC 基功率器件/模块。此外,商用的 GaN 芯片在使用过程中通常将源极与芯片衬底相连,以降低动态导通电阻,获得最好的电性能。因此,在多芯片功率模块的散热设计中,既要保证 GaN 芯片位置合理分布而减小芯片间温差,又要保证基板的线路布局合理降低阻抗,这不同于垂直型Si 基和 SiC 基 MOSFET 器件。最后在封装可靠性方面,虽然 GaN 芯片与封装互连材料间的热膨胀系数(CTE)失配相比于 Si 和 SiC 芯片更小,且 GaN 芯片d性模量比 SiC 低,与 Si 近似,相对不易产生封装互连失效,但以往研究发现在功率循环和温度循环等老化条件下,热失配造成封装互连失效问题依然严重。如表 1 所示为Si、SiC 和 GaN 热导率、杨氏模量和热膨胀系数的对比。这可能是由于 GaN 功率器件/模块的高热流密度带来的大温度梯度加剧了封装连接层产生显著的热机械应力和应变,因此,针对GaN 功率器件/模块的封装可靠性研究仍然非常迫切。

2 封装杂散电感

2.1 杂散电感的来源与影响

杂散电感是由于不同线路之间存在自感和互感现象而呈现出来的等效电感。如图 2 所示,在闭合的电流环路中,变化的电流会产生感应磁场,继而产生感应电动势阻碍原始电流的变化,这就是自感现象。杂散电感是闭合环路的固有属性,有电流通过的地方就有杂散电感,所以只能通过封装技术将其减小而不能完全消除。

杂散电感对 GaN 功率器件/模块产生的影响:降低开关速度,产生开关延时,增加开关损耗。此外,在关断过程中会产生 VGS尖峰电压导致误触发。以 Cascode GaN HEMT 的导通和关断过程为例,分析杂散电感产生的影响。杂散电感使得 Cascode GaN HEMT 在导通过程中,产生导通延时,导通损耗增加。图 3(a)是 CascodeGaN HEMT 电路导通过程示意图。在 Cascode结构中,D 型 GaN HEMT 由 MOSFET 驱动控制,MOSFET 导通,Cascode 结构导通。随着IDS的增大,杂散电感 Lint1和 Lint3会产生与 IDS方向相反的感应电动势,从而导致 VGS_GaN 的变化滞后于 VSD_Si。以 Cascode GaN HEMT 制作的降压变化器为例,在 400V/4.5A 工作条件下导通时,杂散电感使导通时间从 3.5ns 增加到 7ns,导通损耗从 8W 增加到 16W。

杂散电感使 Cascode GaN HEMT 关断过程中,产生 VGS尖峰电压而导致误触发。图 3(b)是Cascode GaN HEMT 电路关断过程示意图。随着IDS的减小,杂散电感 Lint1和 Lint3会产生与 IDS方向相同的感应电动势。由基尔霍夫电压定律得:

VGS_GaN=VSD_Si+VLint1+VLint2+VLint3 (1)

式中 VGS_GaN 是 GaN 的栅-源电压,VSD_Si 是Si MOSFET 的源-漏电压,VLint1、VLint2、VLint3分别是杂散电感产生的感应电动势。以 CascodeGaN HEMT 制作的降压变化器为例,在 400V/12A 工作条件下关断时,虽然 VSD_Si因为钳位作用被限制-30V,但是 VGS_GaN 却产生-5V 的尖峰电压,不仅会造成误触发,还有使栅极被击穿的危险,影响 Cascode GaN HEMT 的可靠使用。因此,要通过合理的封装方法减小杂散电感。

2.2 如何减小封装杂散电感

2.2.1 调整引线级联方式

这种方法主要适用于Cascode GaN HEMT,因为其典型的级联方式是使用引线将MOSFET的漏极、源极分别与D型GaN HEMT的源极、栅极连接。而E型GaN HEMT功率器件/模块不涉及晶体管之间的级联,只有串联或并联的形式,所以无法进一步调整。在功率模块的拓扑电路中,一般将同时存在于功率环路和驱动环路的杂散电感定义为共源极电感(CSI),不同的共源电感对开关速度和开关过程损耗的影响程度是不同的。将共源极电感的概念应用到Cascode GaN HEMT中同样适用。以Cascode GaN HEMT 结构的TO型封装为例,图4是其导通过程的电流流向。从MOSFET的角 度 看 , Lint3和 LS是 共 源 极 电 感 ;从D 型 GaN HEMT的角度看Lint3和Lint1是共源极电感。因此,从整个Cascode GaN HEMT结构来看,Lint3同时是MOSFET和D型GaN HEMT的共源极电感,所以它的影响最大。其次是Lint2,因为它位于D型GaNHEMT的驱动环路中,会影响GaN HEMT的导通速度 。所 以共 源极 杂 散电 感的 影响 程 度依 次为Lint3≻Lint1≻LS。这就为我们提供了解决问题的思路:通过调整引线的连接方式,优先并依次减小共源极电感Lint3、Lint1、LS。

首先,应考虑消除影响最大的共源电感Lint3。例如,2014年,北京工业大学通过改变Lint2的连接方式成功消除了共源电感 Lint3。如图 5(a)所示,引线 Lint2的作用是连接 D 型 GaN HEMT 的栅极与 MOSFET 的源极,使 MOSFET 为 GaNHEMT 提供驱动电压。如图 5(b)所示,现将 D型 GaN HEMT 的栅极与 MOSFET 的源极直接用引线相连,再由 MOSFET 的源极引线连接到源极 的 端 子 处 。这 样 Lint3 被 剔 除 到 D 型 GaN HEMT 驱动环路之外,共源极电感只剩 Lint1。此外,2016 年,韩国电子通信研究院通过在 D 型GaN HEMT 栅极和 MOSFET 的源极之间增加单根引线(Lint4),成功减小了共源电感 Lint3。如图 5(d)所示,增加单根引线 Lint4以后图中的蓝色虚框线内是一个型网络。基于戴维南定理,π型网络和图 5(e)中绿色虚框线内的 T 型网络等效。绿色框线内的等效电感 Lint3’小于 Lint3。结果表明,改变 Lint2的连接方式这种方法简单有效,完全消除了共源极电感 Lint3的影响,而增加单根引线 Lint4只是减小了共源极电感 Lint3的电感值,其影响仍然存在。

其次,按顺序消除共源极电感 Lint1。Lint1的作用是连接 D 型 GaN HEMT 的源极和 MOSFET的漏极。如图 5(c)所示,2016 年,美国弗吉尼亚理工大学将 MOSFET 的漏极直接焊接到 D 型GaN HEMT 的源极上,制作堆叠芯片结构可将Lint1消除。

最后,Cascode GaN HEMT 结构 TO 型封装中共源极电感只剩下 LS。LS是栅极引脚产生的杂散电感,使用 PQFN 型封装可以将 LS消除。此外,如图 5(f)所示,在 PQFN 封装中引入开尔文(Kelvin)电极,可以将 MOSFET 的驱动环路和功率环路解耦,共源极电感只有 Lint3、Lint1,其消除方法同 TO 型封装一致。调整引线级联方式仍然属于有引线封装结构的范畴,要想进一步降低杂散电感,势必要开发无引线封装型式。

2.2.2 无引线封装型式代替引线互连

无引线封装型式对 Cascode GaN HEMT、E型 GaN HEMT 功率器件/模块都适用。键合线产生的杂散电感通常在纳亨(nH)级别。以引线键合封装型式的 TO-220 封装为例,杂散电感≻10nH,这严重限制了 GaN HEMT 在高频下的开关性能。因此,许多研究人员考虑采用无引线封装型式。无引线封装型式能降低杂散电感的原因有二。其一,消除引线,增大了电流流过导体的横截面积,电感减小。其二,减小整个电流环路的面积,电感减小。感应电动势的计算公式如式(2):

式中 Δ∅ 为磁通量的变化量, Δt 为时间的变化量。由此可知,环路面积越小,单位时间内通过的磁感线越少,产生的感应电动势越小,电感越小。

无引线封装型式分为两大类:二维平面结构和三维集成结构。二维平面结构通过增大电流流过导体截面积来降低杂散电感。例如,2016年,美国弗吉尼亚理工大学提出使用薄铜片代替引线的研究设想。2018 年,德国埃尔朗根-纽约堡大学成功使用铜引线框架封装 GaN 功率模块。2020 年,韩国汉阳大学针对平面型 GaN芯片提出全覆盖互连的新概念。其中,薄铜片的横截面积最小,对杂散电感减小的效果最差。铜引线框架在薄片状的基础之上增加了厚度,在降低杂散电感的同时,提升了电极处的散热效率。全覆盖互连结构在铜引线框架的基础之上制作与电极形状相近的图形,以最大的面积覆盖电极,增大电极处导体的截面积,进一步降低杂散电感。图 6 为二维平面结构的发展历程。

由E型GaN HEMT组成的功率模块电流环路中会存在集成电容等分立器件,它们会占据一定空间,要想实现更小的电流环路面积,就要考虑三维集成结构,形成垂直电流环路。图7为三维集成结构的发展历程。例如,2016年,德国弗劳恩霍夫可靠性与微集成研究所开展了GaN芯片嵌入式PCB/DBC混合结构的研究,极大减小了电流环路面积,环路杂散电感可低至0.43nH。2018年,美国东哈特福德联合技术研究中心也开展了将E型GaN HEMT嵌入到多层PCB基板中的研究。但是芯片嵌入式结构的热阻以及制造工艺复杂程度都较高。为了降低热阻以及降低制造工艺的复杂程度,2018年,丹麦奥尔堡大学和2020年,弗吉尼亚理工大学分别针对两种不同的三维集成的芯片非嵌入式结构展开了研究。相比于芯片嵌入式结构,其电流环路的路径以及面积都增大,杂散电感虽然有所增大,但增幅并不明显。目前,美国弗吉尼亚理工大学在2020年提出的PCB插入器式结构是GaN功率器件较为先进的封装结构,能最大限度同时保证低热阻和低杂散电感。

2.2.3 拓扑电路磁相消设计

这种方法同时适用于传统的引线键合封装型式和无引线键合封装型式。前文介绍到杂散电感分为自感和互感。互感是指当一个电流回路中电流发生变化时,其产生的磁场会在临近的电流回路中产生感应电动势,影响其电流的变化。如图8(a), (b)所示是线路 1 产生的磁场对线路 2 的影响。当线路 1 和线路 2 电流方向相同时,线路 2杂散电感为式(3):

L总 = L自 + M 互

当线路 1 和线路 2 电流方向相反时,线路 2杂散电感为式(4):

L总 = L自-M 互 (4)

基于互感的原理,可通过设计使得相邻的电流回路方向相反,这样相邻的两个电流回路产生磁相消,达到降低电感的目的。

拓扑电路磁相消设计主要通过基板实现。在GaN功率器件/模块中常用到以印制电路板(PCB)、直接覆铜基板(DBC)、绝缘金属基板(IMS)三种基板。例如,2013年,美国弗吉尼亚理工大学基于磁相消设计原理,使用PCB基板制作了E型GaNHEMT功率模块,环路电感低至0.2nH。如图9(a)所示,E型GaN HEMT可以和输入电容、驱动芯片等器件放置在PCB基板的上下两面,既能实现磁相消设计,又能缩小电流回路的面积。例如,2014年,美国EPC公司提出了将多层PCB基板的第一内层作为电流的返回路径的方案,可减小电流线路之间的距离,起到增大互感的作用,同时大幅缩短了电流回路的面积。如图9(b)所示。改进后杂散电感从1nH下降至0.4nH左右。同样,2019年,韩国汉阳大学提出了在PCB基板上制作过孔,形成垂直的电流环路的新思路,并在此基础上改进电路布局进一步降低了杂散电感。值得注意的是,PCB基板虽然易于实现磁相消设计,但是热导率低的缺点是限制其在GaN功率器件/模块中应用的主要障碍。IMS基板与PCB基板有类似的地方,它是在金属基板上层压绝缘材料,继而层压铜箔,通过特定工艺在铜箔上刻蚀出一定走线形状。IMS基板根据自身的特点可利用其底部的金属基板进行电磁屏蔽,降低杂散电感的影响。IMS基板不需要复杂的布局和结构设计就能达到低杂散电感的要求,这是其独特的优势[39]。此外,DBC基板也可以通过多层制作实现垂直环路的磁相消设计。例如,2015年,日本富士电机公司(Fuji Electric Company)就利用了垂直环路磁相消的设计原理,已经开展了采用多层DBC封装硅基功率模块的研究。但目前该方法在GaN功率器件/模块中的研究尚未见报道。

2.3 小结与展望

杂散电感严重限制了 GaN 发挥其高开关速度的优势。为了减小杂散电感带来的影响,在GaN 功率器件/模块中减小杂散电感主要有三个思路,分别是调整引线的级联方式、开发无引线封装型式以及通过优化拓扑电路的结构,利用互感的作用降低杂散电感。调整引线的级联方式这种思路只适用于 Cascode GaN HEMT,而且对杂散电感的减小有限,其效果也远低于无引线封装型式。同时,降低杂散电感影响的整个研究历程也是从传统的引线键合封装型式发展到无引线封装型式,在未来无引线封装型式将代替传统的引线键合封装型式。目前 Cascode GaN HEMT 的无引线封装型式只有一种:使用薄铜片代替引线。这种方式对杂散电感的降低效果有限,有待进一步开发更多的针对 Cascode GaN HEMT 的无引线封装型式。E 型 GaN HEMT 功率器件/模块的无引线封装型式目前有很多种,为进一步缩短电流环路的面积,封装结构从二维平面型结构发展到三维集成结构。三维集成结构在降低杂散电感的同时也极大减小了模块的尺寸,具有发展潜力。调整引线级联方式和无引线封装型式这两种方法的思路都是从结构设计上出发,而拓扑电路磁相消设计则是从自感和互感的机理出发降低杂散电感,方法简单、有效。在未来,设计制作三维集成结构,同时对拓扑电路进行合理布局使其产生磁相消,是 GaN 功率器件/模块降低杂散电感的主要研究方向。

3 封装散热设计

以往研究发现,GaN HEMT 的自热效应非常显著。如图 10(a)所示,在 GaN 晶体管中,具有高电子迁移率的二维电子气(2DEG)被限制在AlGaN 和 GaN 的产生的异质结接触面内,这使得其热流密度非常大,尤其在栅极靠近漏极处的狭长区域内,会产生大量的焦耳热。图10(b)—(d)分别为自热效应造成引线的热烧损以及 GaN HEMT 的热击穿现象,需要通过合理设计封装结构,及时将热量从热源位置传递出去。因此,GaN 器件/模块的封装散热设计至关重要。目前针对 GaN 功率器件/模块的封装散热设计可以分为 3 大类:远结被动冷却封装结构、近结被动冷却封装结构、近结主动冷却封装结构。

3.1 远结被动冷却封装结构

被动冷却是通过热传导的方式,靠热量自身从高温物体传递到低温物体,完成散热。在传统的封装结构中,热量传递路径一般经过芯片连接材料、基板、导热胶到热沉,所以又叫远结被动冷却。因此,降低传热路径上各介质的热阻可以增大热量的传递效率。目前在 GaN 功率器件/模块中都是针对封装基板进行改进设计,降低热阻,提升其散热性能。前文介绍到在 GaN 功率器件/模块中,最常用的是印制电路板(PCB)、直接覆铜基板(DBC)、绝缘金属基板(IMS)三种基板。下面分别将三种基板在 GaN 功率器件/模块中应用时的结构设计进行介绍。

制作 PCB 基板的常用材料 FR4 的热导率极低(0.2W/m•K),这是其在 GaN 功率器件/模块中应用的主要障碍。因此,许多研究人员考虑从结构上进行设计,降低 PCB 基板的热阻。例如,2017 年,法国巴黎第十一大学开展了改善GaN 芯片散热性能的优化研究。如图 11(a)所示,增厚 PCB 基板顶部刻蚀电路铜层的厚度可以降低 PCB 基板的热阻。由于 Cu 和 FR4 的热导率差很大,随着铜层厚度的增厚,热量在垂直穿过 FR4 之前,在横向上更加均匀的铺展开,这种结构的横向热扩散效应使得热阻下降。但是当上铜层的厚度超过 300μm 时,热阻降幅将不明显,而且与 DBC 相比,热阻差异仍较大。

如前述,通过增厚 PCB 基板顶部刻蚀电路铜层,可提升热量在 PCB 基板表面的横向传递效 率 。在 此 基 础 之 上 , 在 PCB 基 板 与 GaN HEMT 直接接触的地方制作导热通孔,可以提升热量的纵向传递效率。该设计思路目前主要有两种形式,分别如图 11(b)、图 11(c)所示:PCB基板热通孔设计和嵌入式铜块设计。两种设计的散热性能相差不大,嵌入式铜块设计热阻略低一些。但是嵌入式铜块设计的制作工艺偏复杂,铜块与芯片、铜块与热沉之间的连接界面要保证平坦,孔隙和裂缝的存在都会阻碍热量的传递。相比之下 PCB 基板热通孔技术制造工艺简单,目前应用最为广泛。例如,2011 年,比利时 鲁 汶 大 学 (Catholic University of Leuven, Belgium)提出了在 PCB 基板热通孔中镀金的改良方案,与以往仅使用 LTCC 基板封装相比,GaN 功率放大器的最大输出功率提高近 5 倍。2018 年,威斯康星大学麦迪逊分校的研究团队通过仿真分析研究,发现当 PCB 基板上铜层厚度大于 0.07mm,铜面积大于 4032.25mm2,即使在不使用散热器的条件下,也能保证使用特定BGA 或 LGA 封装的 GaN 集成电机驱动部件在2W 的芯片发热功耗工作时,其壳温不超过150℃,保证模块的可靠使用。2019 年,德国英飞凌公司又基于 PCB 基板易实现多层加工的特点,在热通孔设计的基础上,增加了 PCB 基板中的横向散热路径,进一步提升了 PCB 基板的散热性能,其设计结构如图 11(d)所示。

在 GaN 功率器件/模块封装技术中,DBC 基板因为具有较高的热导率(AlN 陶瓷基板:200W/m•K)而应用最多。在相同试验条件下,GaN 功率模块使用 DBC 基板比使用 PCB 基板可使 GaN 芯片的最大结温下降 136℃。但是在多芯片的 GaN 功率模块中,单面 DBC 结构不能及时将多芯片产生的热量传递出去,热量的叠加使 得 E 型 GaN HEMT 的 最 大 结 温 达 到155℃。长时间的高温工作会加速芯片失效、芯片连接层以及引线的可靠性问题。因此,例如在 2020 年,西安交通大学提出了双面 DBC 的散热结构设计(如图 12(b)所示),该方案可实现上下两部分热阻并联,降低整体封装结构的热阻。双面散热和单面散热的结壳热阻(junctionto-case)分别如式(5)、式(6)所示:

由式(5)、式(6)可知,双面散热模块比单面散热模块芯片结温下降的比率为式(9):

由式(9)可知, (Rth- Σ上部) / (Rth-Σ下部) 越小,结温的下降幅度越大。而对于平面型 GaN 芯片,电极全部分布在芯片的上表面,散热面积小,所以热量大部分向下传递, Rth-Σ下部 小于Rth- Σ上部 。因此,可以通过调整热模块上下两部分的散热条件,来提升芯片结温的下降幅度。

IMS基板在GaN功率器件/模块中使用时,目前未见有独特的结构设计。IMS基板是通过底部金属基板进行散热,表面电路层和底部金属基板之间的绝缘层是热量传递的主要障碍。IMS基板热阻略高于DBC基板,是其热阻的1.5倍;但远低于PCB基板的热阻。值得注意的是,即使使用PCB嵌入式铜块设计,其热阻依然在IMS基板热阻的2倍以上。

将上述 PCB、DBC、IMS 三种基板进行综合比较,不难发现,对于 PCB 来讲,热通孔设计、嵌入式铜块设计与垂直环路磁相消设计很难做到同时兼顾。多层 DBC 的结构虽然能同时保证散热和低杂散电感的要求,但设计复杂且制作难度大。相比于 PCB 基板和 DBC 基板,IMS 基板显示出其独特的优势。它不需要复杂的布局和设计,就能同时实现较低的热阻和较小的杂散电感。这也是目前 IMS 基板并没有独特结构设计的原因。此外,IMS 基板还有较低的制作加工成本以及较高设计灵活性的优势。图 13 从设计灵活性、抗电寄生性能、散热性能、系统成本四个方面,将 GaN 功率器件/模块中常用的三种基板进行了综合比较。

3.2 近结被动冷却封装结构

在前文介绍到的远结被动冷却封装结构中,热量从芯片产生,经过封装基体传递到外界环境。然而对于整个封装体结构,有 67%的热阻来自于芯片以外的封装基体(焊料、灌封材料、基板、导热胶等)。因此,区别于远结被动冷却,许多研究人员考虑近结被动冷却,即通过封装的结构设计,使得热量的传递路径不经过封装基体,一经产生就被热沉传递出去。近结被动冷却主要是通过增加芯片的散热面积达到降低热阻的目的。例如,2012 年,中国台湾交通大学(National Chiao Tung University, China)开展了直接在热沉上连接芯片的研究[49]。如图 14(b)所示,在热沉结构上制作 V 型凹槽,将 E 型 GaNHEMT 置入其中并使用导热银胶填充,通过增加芯片的横向散热路径,增大芯片整体的散热面积。然而通常 GaN 芯片的厚度较小(GaN System公司 GS-065-150-1-D 款 E 型 GaN HEMT 厚度264.5μm),增加的芯片侧面散热面积并不大,同时芯片与热沉结构之间的导热界面材料依然是热量传递过程中的阻碍。所以这种结构的散热效果并不显著。

值得注意的是,近来,扇出式(fan-out)晶圆级封装由于具有更低的热阻,更高的功率密度而备受关注。因此,许多研究人员考虑将 fan-out晶圆级封装的理念引入到 GaN 模块封装中。例如,2012 年,美国休斯研究室直接在 E 型 GaN HEMT 背面电镀金属形成热沉结构。如图14(c)所示,这种结构可以节省导热界面材料的使用,进一步降低热阻,最大可以使芯片结温下降 100℃。2018 年,德国弗劳恩霍夫可靠性与微集成研究所使用扇出型封装形式制作了650V GaN 半桥功率模块。但目前尚未见到对高压氮化镓 fan-out 晶圆级封装的报道。这可能是因为极小的引脚间距尚无法满足高电压下安全爬电距离的设计要求。此外,氮化镓 fan-out 晶圆级封装目前也仅用在低功率场合。虽然在 2020年,德国弗劳恩霍夫可靠性与微集成研究所提出了 GaN 射频功率器件的 fan-out 晶圆级封装设计,并成功研制出实验室样品,但其晶圆级封装器件抗功率循环、抗温度循环的可靠性有待进一步验证。

3.3 近结主动冷却封装结构

首先区分主动冷却与被动冷却:主动冷却通常安装散热部件,借助外力增加热传递的效率。接下来介绍的近结主动冷却是在消除封装基体的基础之上(即近结冷却),增加主动散热的方式。例如,2011 年,日本松下电气公司就已开展了在 GaN 功率器件中使用冷却循环系统的散热研究。2016 年,美国洛克希德·马丁任务系统与训练分公司也开展了 GaN 功率模块中制作嵌入式微流道结构的研究。如图 15(a)所示,嵌入式微流道结构完全消除了金属热沉。通过冷却液直接接触金属衬底将热量带走,可以使芯片结温最大下降 55%。但是微流体对芯片背部的冲击作用不可忽视,它会造成芯片的损伤。如图15(b)所示,将 GaN 芯片封装到一个冷却循环系统框架中可以消除微流体对芯片的冲击。冷却循环系统分为三个部分:蒸发段、冷凝段、回流段。在蒸发段,空腔内部的乙醇液体直接接触芯片的背部,吸收芯片产生的热量蒸发成汽态并挥发到壳体上部。在冷凝段,由于风扇不断向散热片吹入空气进行强制热对流,汽态乙醇受冷重新凝结为小液滴。在回流段,冷凝后的乙醇小液滴受壳体内部针状结构毛细吸引力作用,汇聚到回流通道,形成大的乙醇液滴并流回蒸发段,这样形成一个循环。如此不断重复,完成冷却循环系统的导热过程。该结构与传统的封装结构相比,热阻下降 32%。近结主动冷却封装结构能极大降低封装结构的热阻,但往往尺寸较大,且设计制造复杂。

3.4 小结与展望

远结冷却结构与近结冷却结构的本质区别是:热量经芯片产生传递到热沉的过程中是否通过封装基体。近结冷却相比于远结冷却,消除了封装基体,极大降低整体结构的热阻。主动冷却相比于被动冷却,使用液冷的方式提升了热量的传递效率。远结被动冷却结构主要着重于对基板的改进设计。PCB 基板遵循着从增强表面横向散热、增强纵向散热到横向散热和纵向散热混合使用的设计思路。DBC 基板则主要着重于开发双面散热结构。近结被动冷却结构遵循增加芯片散热面积的思路,从基板上制作 V 型凹槽到在芯片背部直接电镀热沉结构的 fan-out 晶圆级封装,都通过增加芯片的侧向散热路径来增大芯片的散热面积。制作 V 型凹槽这种方法由于芯片厚度小,且芯片与热沉之间的导热胶阻碍热量传递,对散热性能提升的效果并不显著。近结主动冷却结构设计了嵌入式微流道和冷却循环系统两种结构,虽然极大降低了结温,但是这两种结构尺寸大、制作复杂,抗机械冲击可靠性低。

综上所述,远结被动冷却仍然是 GaN 功率器件/模块主要使用的封装结构。其中双面 DBC散热结构因具有更低的热阻,将会成为主流的封装结构。

4 封装连接可靠性

GaN 功率器件/模块的封装连接可靠性风险主要集中封装连接层。包括连接层材料的开裂,引线键合脱落或断裂等。失效产生的原因是连接层材料和引线键合界面的热机械疲劳损伤。此外,考虑到 GaN 的耐高温应用特性,随着工作时间的增加,连接层材料会产生热蠕变疲劳损伤。而在实际的工作过程中,热机械疲劳损伤和热蠕变疲劳损伤会产生耦合作用。热蠕变促进了连接层材料微裂纹的萌生和扩展,热机械应力又提高了热蠕变的程度。这种耦合作用会加剧连接层材料失效的风险。因此,本文接下来将主要介绍如何提高 GaN 功率器件/模块封装连接层的热机械疲劳失效与热蠕变疲劳失效抗性。目前未见对 GaN 功率器件/模块中引线失效以及增强引线失效抗性的相关报道。

4.1 热蠕变疲劳失效

对于大多数连接材料来讲,在长时间的高温工作过程中会有蠕变疲劳失效的风险。工作温度为0.6Tm是连接材料蠕变变形的临界状态(Tm:焊料熔点),当温度超过0.6Tm,蠕变变形机制开始起作用,并逐渐占据主导地位;当工作温度超过0.8Tm,连接材料会因为蠕变造成晶界滑移,产生塑性变形而快速开裂失效。目前,在低温段工作的GaN功率器件/模块中常用的高温焊料是金基焊料和高铅焊料。然而随着研究的不断进展,最新研制的GaN HEMT可以在325℃下稳定工作,所以要求芯片连接材料的熔点至少在400℃以上。如图16所示,在功率器件/模块中常用的金基焊料都不能满足更高的工作温度要求。同时,合金焊料在长时间的高温工作条件下,连接 界 面 处 脆 性 金 属 间 化 合 物 生 长 严 重 。以Au80Sn20为例,在240℃条件下保存72h,脆性金属间化合物Au-Ni-Sn生长大约1.6m,造成连接层抗剪强度的下降,进一步增加了连接层热蠕变疲劳失效的风险。此外,由于ROHS指令对焊料无铅化的要求,高铅焊料也会被逐渐替代。因此,目前迫切需要开发熔点更高,同时在高温下保证高可靠性的焊料,以充分保证GaN器件/模块的工作可靠性。

在 GaN 功率器件/模块中,目前流行的两种芯片连接技术是瞬时液相 (Transient liquid phase, TLP) 连 接 和 低 温 连 接 技 术 (Low temperature joining technique, LTJT)。其中瞬时液相连接技术以锡银的瞬时液相 (简称 Sn Ag TLP)连接应用最多,低温连接技术以烧结银应用最多。

TLP 连接技术通常是指在连接金属表面镀覆低熔点金属作为中间层材料,在适当压力下加热至熔点。低熔点中间层材料和高熔点金属发生固-液互扩散现象,生成高熔点的连接层,实现低温连接、耐高温工作的应用条件。当使用Sn、Ag 作为中间层材料时,Sn 在熔点 232℃下熔化并扩散到 Ag 中与 Ag 生成高熔点的二元合金ζ相 Ag85Sn15(Tm≻600℃),连接界面完整、无孔洞,而且不需要助焊剂。例如,2015 年,德国弗莱堡大学最先开展了 Sn Ag TLP 连接在GaN 芯片封装中的应用研究。然而该方法成本高、时间长,不利于商业化应用。对于 Sn Ag TLP 连接在 GaN 功率器件/模块中的应用研究尚处于起步阶段,目前未见对其高温蠕变疲劳失效的研究报道。这可能与生成的金属间化合物具有较明显脆性,疲劳失效的风险仍然显著有关。

近年来,LTJT 技术,尤其是低温烧结银连接技术受到广泛关注。烧结银以其 961℃的高熔点,低焊接温度的优势,成为替代 Au80Sn20 和高铅焊料、应用在 Cascode GaN HEMT、E 型GaN HEMT 功率器件/模块中芯片连接的主要候选 材 料 。早 在 2013 年 , 天 津 大 学 (Tianjin University, China)就开展了烧结银在高温下的蠕变疲劳行为研究。研究证实烧结银具有较高的热蠕变疲劳失效抗性,适合在 GaN 功率器件/模块中使用。

4.2 热机械疲劳失效

如图 17(a)、(b)所示,由于不同材料的热膨胀系数不同,在温度的变化过程中,材料的收缩程度就会不同,在界面处会产生交变的热机械应力。热机械应力的表现形式是平行于连接界面的剪切力。剪切力又会使不同材料产生不同程度的塑性变形。随着循环次数的增多,连接层界面材料塑性变形不断累积,产生热机械疲劳失效。在 GaN 功率器件/模块中,由于 CTE 不匹配造成界面开裂失效的位置有两处,芯片与基板连接层以及 DBC 基板的铜与陶瓷连接层。对于芯片与基板连接层如图 17(c)所示,其应力和塑性功密度的最大值位于芯片连接层靠近 DBC 的边角处。因此,此处最易萌生裂纹,造成分层开裂现象。对于 DBC 基板,如图 17(d)所示,其在高温使用的过程中,高温工作条件下易发生铜层脱落的现象。此外,从图中可以看出 DBC基板的氧化现象十分严重。

值得一提的是,前文提到的烧结银和Sn AgTLP都具有非常高的热机械疲劳抗性,可以有效的抑制芯片连接层发生分层断裂。在温度循环老化条件下,烧结银的可靠性都要优于Au80Sn20和Pb5Sn焊料,因为温度循环次数的增加,烧结银接头的烧结颈不断变粗,使得接头的连接强度变大。如图18(a)—(c)所示为烧结银接头在温度循环作 老 化 条 件 下 烧 结 颈 不 断 粗 化 的 现 象 。而Au80Sn20、Pb5Sn接头在温度循环的过程中,脆性金属间化合物生长加厚,从而造成接头的抗剪强度的下降。如图18(d)—(f)所示为Pb5Sn接头在温度循环老化条件下界面金属间化合物增厚同时出现孔洞的现象。2015年,德国弗莱堡大学将低温烧结银连接和Sn Ag TLP连接在可靠性方面进行了比较,两者在功率循环和温度循环作用下都表现出优异的可靠性,且优于金基焊料和锡铅焊料。

为了抑制芯片连接层的断裂,2018年,日本大阪大学从芯片连接层的结构上进行改进,提出了烧结银-W-烧结银的三明治式结构[28]。图19是芯片连接层从高温冷却至室温时的应力变化行为,利用W薄膜高d性的特点,使其分担芯片连接层和基板界面处的界面应力,同时使得烧结银和基板连接界面处的应力方向重合,界面处材料的塑性应变下降大约50%。

为了抑制 DBC 基板在使用过程中发生铜层脱落的现象,2018 年,日本大阪大学开展了GaN 模块中 DBA 基板表面镀 Ni 的应用研究。如图 20(a)、(b)所示,将 GaN 芯片连接到DBA 基板上后,发现在温度循环老化条件下DBA 基板开裂。这是因为 Al 晶粒在高温作用下会粗化长大,而且铝的杨氏模量低,容易发生塑性变形。这使得烧结银和 DBA 基板的连接界面在工作中会有裂纹萌生并扩展,从而造成界面开裂现象。为此,作者在 DBA 基板表面镀厚Ni 层(7μm)。如图 20(c)、(d)所示,Ni 在高温作用下,晶粒长大的不明显,可以抑制 Al 晶粒的粗化。在 GaN 功率器件/模块中使用 DBA 基板表面镀 Ni 代替 DBC 基板,避免了基板铜层脱落的风险,同时提高了连接界面的可靠性。

4.3 小结与展望

为了解决热蠕变疲劳失效的问题,研究人员已提出了采用低温烧结银连接材料技术和 Sn AgTLP 连接材料技术。这两种材料同时具有较高的热蠕变疲劳以及热机械疲劳失效抗性,应是未来研究的热点。为了解决热机械疲劳失效的问题,研究人员还提出改变芯片连接层的结构以及在基板表面镀 Ni 两种方法。“Ag-W-Ag”三明治式结构虽然能大幅降低界面处连接材料的塑性应变,但结构复杂,实际 *** 作困难。DBA 基板表面镀Ni 这种方法简单有效,明显降低了基板表面附层脱落的风险。

5 GaN 功率器件/模块封装技术的思考

尽管 GaN 功率器件/模块的封装技术是当前研究热点,在降低杂散电感、封装散热结构设计和提升封装连接可靠性等方面也已引起广泛关注 。2018 年 , 美 国 阿 肯 色 大 学 (Uniersity ofArkansas, USA)研究团队[65]最先发表了先进 GaN器件封装与集成研究综述,从芯片级封装、模块级封装与集成和封装热管理三个方面提出 GaN封装技术面临的挑战,并指出当下需要重点研究的三大问题:(1)降低 GaN 器件功率环路和驱动环路的杂散电感;(2)优化 GaN 集成模块开关性能;(3)提出更有效的热管理方案。目前,针对这三个问题都有许多效果显著的解决方案,已经在文中进行阐述。然而仍存在大量亟待解决的问题以及研究空白,处于刚起步阶段。

1)双面 DBC 散热结构、芯片嵌入式结构和带有 PCB 插入器的 GaN 功率器件/模块存在可靠性瓶颈。这是因为这三种结构都是目前较为先进的封装结构,同时具有较低热阻、低电感的优良特性,但由于结构复杂,会增大整个封装体的内应力,降低其可靠性。使用 CTE 相匹配的封装材料或使用合适的灌封材料做缓冲层也许是有效的解决方案。

2)亟待开展 Cascode GaN HEMT 的双面散热结构的开发与封装可靠性研究。其中 E 型GaN HEMT 表面复杂的电极形状是其实现双面散热结构的最大阻碍。采用芯片嵌入式封装的方法实现双面散热或许是可行的方案。

3)亟待揭示 GaN 功率器件/模块中连接层材料与引线在热蠕变疲劳和热机械疲劳耦合作用下的失效模式、失效机理以及显微组织变化等。但是由于热蠕变和热机械应力耦合的试验条件难以实现,目前对于这一部分的研究仍是空白。可以考虑先从仿真研究入手,提供物理模型和仿真数据,为以后的试验研究打下基础。

4)亟需探索 GaN 功率器件/模块中引线失效形式以及提升其可靠性的方法。尤其值得注意的是,GaN 功率器件/模块的耐高温应用特性会增大引线产生热蠕变损伤的风险,聚焦其在高温下的蠕变疲劳行为开展研究更有研究价值。具体研究可以沿着温度梯度对引线与基板连接界面上晶粒塑性变形程度影响的路径去探索。

不难发现,问题(1)、(2)、(3)都是有关 GaN基功率器件/模块无引线封装型式可靠性方面的问题,是这一领域亟待解决的最关键问题。因为目前研究人员在追求 GaN 功率器件/模块的低杂散电感封装、低热阻封装型式的时候,往往并不能同时兼顾其在可靠性方面的性能,导致这些研究成果并不能很好的商业化应用。因此,解决新型 GaN 功率器件/模块封装型式的可靠性问题对于推进科研成果产业化具有重要意义。相比之下,问题(4)属于次要关键问题,因为该问题是关于引线键合封装型式的 GaN 功率器件/模块中引线的可靠性问题,然而目前引线在 GaN 器件/模块中使用频率越来越少,将来势必会被无引线封装型式取代。

审核编辑:汤梓红

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)