问:通过LC滤波器,来改善高速DAC电源相位噪声

对于高速DAC供电电源的选择,LDO是久经考验的稳压器,尤其适合用来实现优质噪声性能。相关技术资讯,可参阅文章:选择超低噪声的LDO来改善相位噪声 。

但是并非只能选择LDO而别的电源不可以用,根据整体系统要求,通过适当的LC滤波,开关稳压器也可提供电源解决方案,从而简化电源解决方案。

但由于采用LC滤波器,所以应注意串联谐振,否则噪声可能变得更糟。对于谐振可通过降低电路Q值来实现——通过为电路增加损耗性元件,加以控制。

下图显示一个设计实例,其采用AD9162 DAC,时钟电源也是由ADP1740 LDO提供,但其后接了一个LC滤波器。

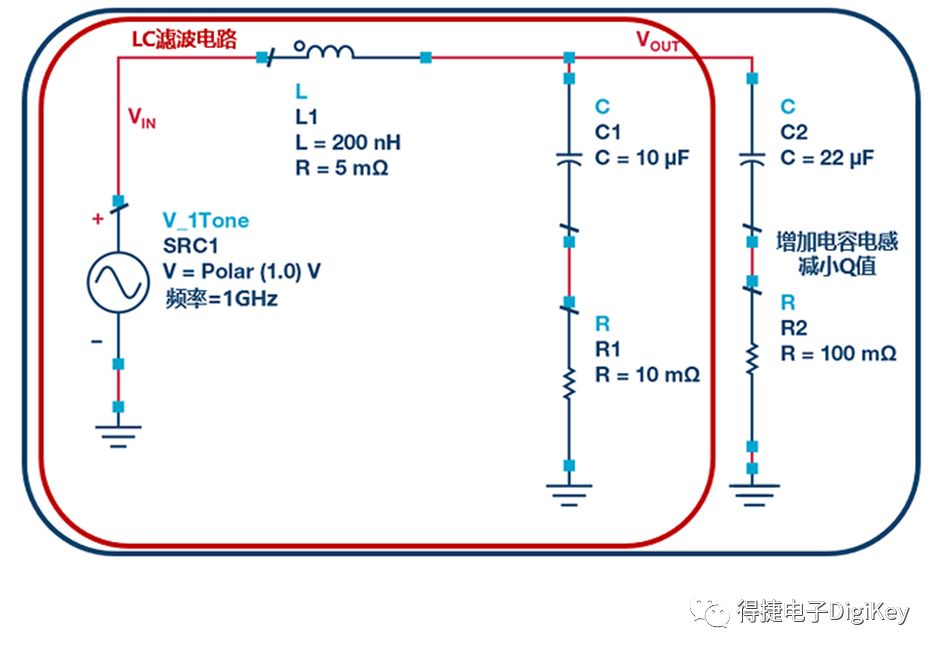

图1:LC滤波器和去Q网络

原理图显示了所考虑的滤波器,RL模型表示电感,RC模型表示主滤波电容(C1+R1)。红圈里是原始的LC滤波电路,蓝圈是为了减小Q值额外增加的损耗性元件。

图2:LC滤波器响应

滤波器响应如下图所示,红线是原始的LC电路响应曲线,蓝线是改进后的响应曲线。我们看到Q值减小了。

图3:相位噪声响应

我们再来看看,对于相位噪声响应,蓝线是原始的LC电路响应曲线,橙线是改进后的响应曲线。可见,相位噪声得到改进。

总之,噪声不仅会因为电源选择的不同而有差异,而且可能受到输出电容、输出电压和负载影响。因此设计时应当仔细考虑这些因素,尤其是对于敏感的供电轨。

审核编辑:汤梓红

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)