为了做一些有用的事情,微控制器 (MCU) 必须连接到其他设备。此连接是通过输入/输出 (I/O) 引脚进行的。很多时候,现在的引脚是多功能的,可以连接到 A/D、D/A、线性功能(例如运算放大器和比较器)、电压基准等。因此,对于设计工程师来说,保护这些 I/O 免受潜在的破坏性静电荷和其他类似威胁非常重要。

在为 MCU 建立适当保护时,工程师发现他们多年来依赖的特性突然变得不那么有效,他们不得不重新审视过去的问题。为什么?主要是,由于降低产品成本的市场压力,半导体制造商将更高的集成度与工艺几何尺寸的持续缩小相结合,使芯片尺寸更小。因此,实施必要的瞬态抗扰度保护以防止由于电源和信号线上的瞬变引起的故障变得越来越困难。

当几何形状和 IC 特征尺寸更大时,I/O 焊盘有很大的面积用于驱动器,并能很好地防止 ESD 引起的损坏。在努力提高良率的过程中,使用了更小的芯片和焊盘,就其性质而言,它们不太可能受到撞击以保护微器件。根据经验,静电电荷总是会通过最短的路径产生电弧,而精密的微型 I/O 线路会导致更多的静电放电命中通过。

本文着眼于 MCU 对电气快速瞬变 (EFT)、静电放电 (ESD) 和其他短期事件的不同级别的抗扰性,并提出了实用的硬件和设计技术,这些技术可以提供具有成本效益的方式来保护微控制器 I/O线。

免疫性能

人们可以将瞬态威胁分为三种主要类型:静电放电 (ESD)、电快速瞬态 (EFT) 和浪涌瞬态。为确保电路对这些瞬态的稳健性,国际电工委员会 (IEC) 在其 IEC61000-4 系列电磁兼容性 (EMC) 标准中指定了一系列瞬态抗扰度测试:IEC61000-4-2 涵盖了 ESD 抗扰度(适用于手持设备IEC61000-4-4 对 EFT 抗扰度的作用相同,IEC61000-4-5 处理浪涌抗扰度(闪电和工业浪涌)。

集成电路的抗扰度性能进一步分为 IEC 文件 ( IEC 62132-1 ) 中规定的四个类别之一。¹ A 类性能定义为瞬态应用期间在规范限制内的正常性能。B 类性能是暂时的降级或功能或性能损失,在瞬态消除后可自行恢复。C 类性能定义为在瞬态消除后需要 *** 作员干预或系统重置的暂时性降级或功能或性能损失。D 类性能是由于数据损坏或丢失而无法恢复的永久性降级或功能丧失。

各种标准组已经使用标准化测试和监测分析了瞬态电压的发生,并已根据条件特性就所需的多个保护级别达成一致(表 1)。考虑到用于这些应用的驱动器、I/O 晶体管和半导体类型的特性和限制(表 2)。

表 2:设备接口技术敏感性特征。

除其他因素外,受 ESD 或 EFT 事件影响的 MCU 性能受其工艺技术、IC 封装、印刷电路板 (PCB)、MCU 上运行的软件以及 ESD 或 EFT 事件特性的影响。

像TMS320F28035PAGT这样的德州仪器微控制器将符合 IEC 标准,但仍然会因大量的充电而受到破坏,尤其是在连接到 SD/MMC 卡、USB、IEE1394 和千兆以太网等应用的电缆和连接器时。

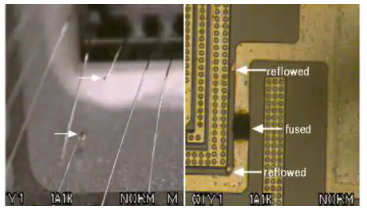

汽车应用也可能引入高压放电。飞思卡尔半导体MCU(例如MCF5329CVM240)利用了公司及其前身(摩托罗拉)在军事和航空航天强化处理器发展过程中进行的广泛测试和故障分析。他们已经将电过应力 (EOS) 的两种失效机制隔离为施加到引脚上的总能量的函数。在一种情况下,可以熔断键合线,如果键合线可以将电荷传送到内部 I/O 焊盘,则可以进行熔丝管芯金属化(图 1)。

图 1:如果允许通过,即使有内部保护,低至 1 A 的电流也会导致芯片线熔断和基板金属化。

像STMicroelectronics这样的微控制器制造商使用他们自己的各种测试系统(如快速瞬态突发 [FTB] 测试仪)来测试STM32F429IIT6等 MCU ,它具有高性能 ARM® 32 位 Cortex™-M4 处理主干,可以连接到几个可能对 ESD 敏感的外部 I/O 结构。

对于其STM8S 8 位 MCU 系列,ST 在产品表征期间以样本为基础进行敏感性测试。对于功能性 EMS,在执行一个简单的应用程序(通过 I/O 端口切换两个 LED)时,产品会受到两个电磁事件的压力,直到发生故障(由 LED 指示)。对于 ESD,静电放电(正和负)施加在器件的所有引脚上,直到发生功能干扰。该测试符合 IEC 61000-4-2 标准。对于 FTB,快速瞬态电压(正和负)通过一个 100 pF 电容器施加到 VDD 和 VSS,直到发生功能性干扰。该测试也符合 IEC 61000-4-4 标准。

设备复位允许恢复正常 *** 作。测试结果基于应用笔记 AN1709 中定义的 EMS 级别和类别。²

所有 MCU 供应商都使用谨慎的设计实践来降低其产品对 ESD 事件的敏感性。然而,正如Microchip Technology在其应用笔记 AN595 中所指出的,³保护级别因引脚而异,反映了每个引脚的不同功能。某些类型的引脚(特别是电源引脚)比其他引脚更容易受到 ESD 脉冲引起的闩锁的影响。这是由于不同的设计和布局考虑降低了 ESD 保护的有效性。

因此,虽然具有高 EMC 抑制能力的 IC 减少了对外部元件的需求,但片上 IEC-ESD 保护通常对实验室和便携式设备有利,这些设备很可能因人体接触连接器和电缆而发生放电事件,但也可以不足以应对工业环境中发生的 EFT 和浪涌瞬变。因此,稳健可靠的设计可能需要外部瞬态保护器件。

保护解决方案

防止持续时间非常短的非常高瞬变的最古老但仍然最有效的技术之一是限制高压条件下的浪涌电流。虽然较小的焊盘在物理上无法处理较大焊盘可以处理的电流密度,但它们可以在其范围内可靠地分流电源而不会损坏。外部无源在这里可以非常有用地减弱和减缓破坏性水平。

具有灾难性 I/O 焊盘故障模式且接地短路的典型 3.3 V 系统可以使用 22 Ω 串联电阻器来限制电源电流。在许多非高速应用的正常 *** 作期间,串联电阻不会影响性能。在短路故障期间,当电源短路时,½ W 22 Ω 电阻器会将电流限制为 150 mA。这仍然是系统故障,但不太可能着火。

串联铁氧体还可用于抑制电流的瞬时突增,它们还具有衰减高频 EMI 和 RFI 的额外好处。但是要小心,因为这些“本质上是感应的”部分会在某些条件下引入尖峰。

这些无源低成本解决方案对于 V CC故障和相当低的电压但潜在的大电流故障非常有效。然而,高压尖峰可以而且确实会造成严重破坏。例如,即使是我们的 22 Ω 示例,在典型的 8 kV 静电放电期间仍允许 363 A 的瞬时电流。在这里,并联电容还可以通过将其从微控制器的 I/O 线分流来限制浪涌电流(图 2)。

图 2:无源 R/C 时间常数可用于限制上层尖峰,直到响应较慢的抑制器可以接合。请注意,耗散的能量是相同的(曲线下的面积)。

请记住,静电放电通常是非常快的事件。因此,电容器不必存储大量电荷。事实上,您不需要大电容。它会扭曲信号并降低数字性能。它只需将电压上升速度减慢到足以让电路以更可控的方式吸收能量即可。这对于在某些汽车设计等可能充满 EMI 的环境中的低速信号来说很好。

无数分立器件甚至 R/C 阵列都可用于挖掘可能暴露的多条 I/O 线。这些可以与可以快速吸收和分流更高电平的半导体瞬态电压抑制技术结合使用;您想要快速的响应时间。我们的 22 Ω 示例暴露在 8 kV 的震动下,当短路到地时,将消耗几乎瞬时的 3 MW 功率。

对于大多数正常环境,静电荷不应超过 15 kV(但当条件恰到好处时,我们都对比平常更高的冲击感到惊讶)。这就是为什么经常需要保护多条 I/O 线的原因,即使它们不耦合到外部导体。小引脚间距可以让电弧跳跃。德州仪器 (TI ) 的通用TPD4E001 ESD 保护阵列等多通道 ESD 器件可在此提供帮助。TI TPD4E001DRLR等部件可提供 30 kV 范围(+15 至 –15 kV)的双向保护。

除了通用部件外,还提供用于设计的专用器件,例如用于 USB 充电器端口保护的 TI TPD4S014DSQR ,或用于 VGA 端口保护的供应商TPD7S019-15DBQR 。

Tyco 还从其TE ConnecTIvity部门提供满足这一需求的零件。TE 的硅 ESD 系列 (SESD) 的尺寸比前几代产品更小,最新的 0201 尺寸部件具有极低电容 (0.6 pF) 和可选电压响应范围的系列成员。单通道、双通道、四通道和六角通道部件有助于空间狭小。

例如,查看SESD0402P1BN-0450-090。该器件具有 6 V 的反向电压隔离水平。当暴露于典型的 8 kV ESD 事件(图 3)时,它会非常迅速地达到 9 V 击穿电压,并在高达 2 A 的浪涌下非常有效地钳位在 12 V(图 4) .

图 3:典型的 8 kV ESD 事件会迅速出现尖峰,但在达到峰值之前被切断。在纳秒内,浪涌已经稳定,瞬态电荷已经放电。

图 4:在承受 ESD 事件时,击穿发生的速度足够快,可以钳位在或低于额定水平。

结论

在将数字电路与外界连接时,必须小心保护敏感的电子设备。长期以来,工程师一直让微控制器供应商为 I/O 线提供固有保护。虽然它们做得很好,但电子设备越来越容易被 ESD 干扰。

既然裸片尺寸与以前的 I/O 焊盘一样大,我们可能需要外部保护,尤其是 ESD 保护。幸运的是,如果您知道在哪里寻找,有几种技术可以提供解决方案。在大多数情况下,提供必要保护所需的电路体积小、价格便宜且易于理解。总体而言,MCU 保护只需要在设计系统时进行一些深思熟虑,以避免系统部署后的诸多困难。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)