Cadence CDNLive:搭建沟通平台,加速设计创新

“工程师是最终决策的源泉。通过设计自动化,让决策者做出的每一个决定不但高效正确,而且充满意义和乐趣,这就是我们存在的价值。”Cadence公司总裁兼CEO Michael J. Fister近日在CDNLive China上这样表示。

作为Cadence公司最重要的全球性技术会议,每年一度的CDNLive都将广大电子设计师和工程师汇聚在一起,共同分享最新的设计技术与挑战,倾听关于市场变革与创新的最新理念。本文将力图从不同角度与读者共享此次会议的成果。

加速设计创新

半导体供应商目前正面临着设计复杂度所带来的世界级挑战。因此,Cadence在年初就勾画了其扩张到系统级相关领域的战略。Fister强调说:“复杂性驱动着混合信号设计、芯片规划解决方案,以及更高水平设计的实现,只有不断推出生产力最优化的解决方案,才能减少客户在系统规格与设计实现之间的反复,提高设计师在创建和复用系统级芯片IP过程中的效率。”

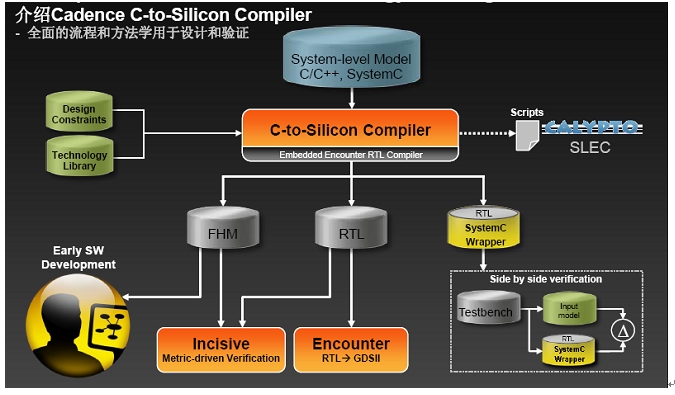

作为C++adence系统级战略的首款产品,C-to-Silicon Compiler在此次CDNLive上被隆重推出。Cadence称,该产品可以自动转化和优化从C/C++、SystemC,到可综合的Verilog RTL(包含断言)所描述的提取行为,进行实现、验证和SoC集成,能够将现有生产力提高10倍。而且具有嵌入式逻辑综合和支持验证这两个比较突出的特点。

下一代SoC技术的特性

清华大学魏少军博士在其主题演讲中指出,摩尔定律将长期有效,等比例缩小在成本下降方面的作用已开始显现。而随着消费类电子成为集成电路的新驱动力,架构创新已经刻不容缓,软件在芯片设计中的作用日益凸现,培养软件工程师成为当前最紧迫的工作。“我们可能愿意花钱雇一个销售的高手,但更愿意花钱雇一个芯片设计的高手。”魏少军表示。

因此,EDA工具的发展对半导体行业而言是至关重要的。他强调说,半导体工艺每前进两个节点,就要求有新的EDA工具出现。主流EDA工具目前在很大程度上仍围绕PR竞争,低功耗设计在EDA层面也面临很多挑战,所以业界普遍希望出现软件设计自动化的集成工具。以低功耗作为突破口,关注移动通讯和互联网的发展,将是未来设计发展的主流。

多项技术意欲展现实力

数模混合信号是目前造成芯片流片失败的主要原因之一,例如递增的模拟控制信号对功能的影响、通过数字控制信号对模拟电路微调,以及数字和模拟电路接口信号的验证等等。Cadence公司模拟部门副总裁刘志宏表示,为了应对这些挑战,Cadence已提出了全面的解决方案,包括模块级模拟功能。例如Spectre 及“Turbo”技术、数模混合功能和性能;全能FastSPICE仿真技术,覆盖了UltraSim、全芯片数模混合功能、以及晶体管级功耗、EM/IR、可靠性分析;数模混合逻辑验证环境,包括Incisive逻辑验证、支持多设计语言和验证方法、命令行数模混合严正流程。

而Cadence公司高级验证R&D副总裁Apurva Kalia则介绍了在SoC芯片设计中,如何通过指标驱动验证(Metric Driven VerificaTIon)将想象转化为现实。首先,团队根据需要创建项目;随后,验证引擎开始执行,产生的测量指标由指标驱动的过程自动化解决方案收集,并提供给团队进行分析;最后,经过对排列优先权、资源再分配及其他自动调试场景执行后,项目开发周期结束。“设计和验证团队成员并肩工作是非常重要的。”他强调说。

另据调查显示,运行时间和容量、时效分析及优化、低功耗设计、MulTI-code/corner优化和时序收敛,以及工程变更指令(ECO)是目前IC设计中遇到的突出问题。Cadence 公司IC数字工程副总裁Frank Leu在主题演讲中阐述了Encounter平台的优势。他介绍说,通过提供一个从RTL综合和测试设计,到芯片虚拟原型和分割,再到最终时序和制造收敛的完整流程,Cadence帮助工程师提升了在芯片(时序、面积、线路功耗)、精确验证、注重信号完整性的布线,以及在65/45纳米设计中高成品率方面的能力。

收购Mentor Graphics,利还是弊?

Cadence不久前曾提议以16亿美元的价格收购Mentor Graphics,但一些业内人士却认为这不是什么明智的决定。“Cadence和Mentor这两个公司在合并后没有什么新的优势,因为两者在很多方面有重叠,合并只会导致共同负债增多。”Gary Smith EDA首席分析师Gary Smith指出,“将两家公司绑在一起的结果是最后大家都可能完蛋。”

但Cadence却不赞同上述说法。“做出这样的收购建议,也是经过慎重考虑的,我们认为这样做是对的,并希望这能给Cadence带来积极的影响。”Fister在接收本刊记者专访时这样表示,“现在这个程序已经开始了,我们在等待下一步结果如何”。

Fister解释说,客户在面对来自成本、业绩、效率、市场推广等诸多方面的压力情况下,需要设计公司提供最优化的、系统级的解决方案,然而大多数EDA公司却只提供了其中的一部分,并没有提供更多的整体方案,Cadence提议收购Mentor,就是为了给客户能够提供更有效的环境,给股东提供更高的利益。

近期,Cadence参与了许多收购。例如,在2008年3月,Cadence收购了Chip EsTImate 公司,这是一家IC规划和IP复用管理工具的开发商;5月,收购了专业光刻公司Invarium;

2007年8月,还收购了一家可制造性设计(DFM)技术的开发商Clear Shape Technologies。

对国内IC设计公司的建议

尽管中国IC设计公司在过去的数年中已经取得了长足的发展和进步,然而相对于领先的国际半导体公司来说,无论在规模还是在技术上,本土公司都无法与之相提并论。

站在EDA厂商的角度,Fister为本土IC公司提出了以下三条建议:一、半导体行业发展不能禁锢于过去的历史,而要采用全新的模式。二、从考察潜在合作伙伴的财务状况、技术实力、甚至是全球分布情况入手,尽早与之结成伙伴关系。三、无论现在市场地位如何,要未雨绸缪,及时总结经验教训,积极考虑公司未来的发展方向。

而Cadence公司亚太区总裁、全球副总裁居龙则表示,Cadence的低功耗解决方案、模拟混合信号解决方案、功能验证解决方案特别受到本土工程师青睐。针对中国市场,2008年Cadence将重点开发模拟混合信号、低功耗、先进工艺节点和从计划闭合等四大领域,籍此帮助国内客户构建差异化竞争优势。此外,他也特别强调了拥有自主IP,以及在生态系统中寻找合作伙伴的重要性。

Cadence C-to-Silicon Compiler

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)