在基于IP核复用技术的集成电路设计中,片上总线的选取是最为关键的问题。目前,许多厂商已经开发了适用于各自片上总线标准的UART IP核,例如基于AMBA总线的UART IP核、基于CoreConnect总线的UART IP核等。如果用户要使用这些商业化的UART核,则需要得到授权。因此从成本、性能、开放性的角度来看,采用开源、易于实现的Wishbone总线标准设计出的UART IP核将会拥有广泛的市场。

1 UART IP核的设计原理

1.1 UART工作原理

通用非同步收发装置(UART)是计算机进行串行通信的重要组成部分。它将微机系统内部传送过来的并行数据转换为串行输出数据流,以电平的形式传输出去;将微机系统外部传送来的串行数据转换为字节,供微机系统内部使用并行数据的器件使用;在输出的串行数据流中加入奇偶校验位,并对从外部接收的数据流进行奇偶校验;在输出数据流中加入启停标记,并从接收数据流中删除状态标记。

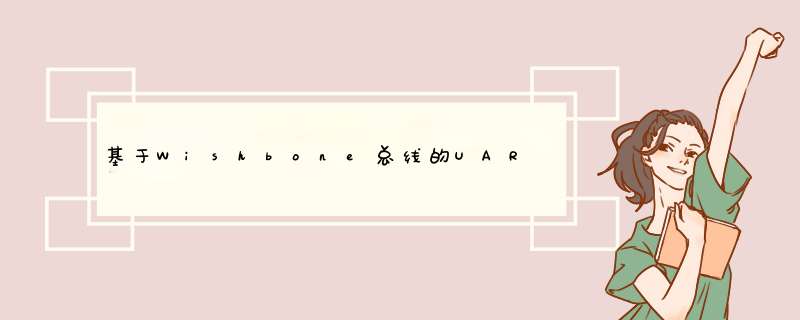

对于UART而言,总线上的所有信号都是至关重要的。这些信号包括所需的控制信息和数据。因此总线接口的设计决定着UART的设计细节。本设计采用Wishbone总线作为UART核与微机系统进行通信的主机接口。UART核的接口信号如图1所示。

1.2 Wishbone总线接口

在集成电路设计领域,Wishbone总线结构是一种灵活、开源的设计方法。其目的是促进设计的再利用,简化系统级芯片的集成问题。通过在IP核之间创建一个总线接口,从而将各个IP核能方便地进行连接。这就提高了设计的可复用性和系统的可靠性,加快了产品推向市场的速度。在此之前,IP核之间都是使用非标准的总线规范进行连接的,这就难以实现复用。因此采用标准化的E总线结构设计IP核,已成为IC设计行业的主流。

在设计中,Wishbone总线为微机系统和UART控制器提供了 *** 作接口。Wishbone总线接口的主要功能是协调处理器和UART核之间的信号,使处理器能正确地使用UART核进行数据通信。

2 UART IP核的设计实现

UART IP核的研发是遵照RS232协议和Wishbone总线标准进行的,集成了UART的基本功能。

UART IP核的主要技术特征包括:

(1)支持标准RSR232接口标准和Wishbone总线规范。

(2)全双工独立收发功能。

(3)接收通道进行奇偶校验,溢出,产生可选中断。

(4)内置支持接收和发送的16 Byte FIFO。

(5)发送“空”产生可选中断,接收“满”产生可选中断。

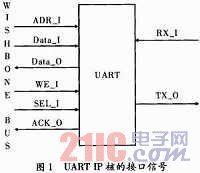

UART IP核体系结构如图2所示。

UART IP核内部主要包括数据发送模块、数据接收模块以及Wishbone总线接口模块。各模块的设计如下。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)