本文提出采用"NiosⅡ+AT24C02"设计方案,在介绍AT24C02A芯片主要特性和分析I2C通信协议原理基础上,重点介绍Nios Ⅱ与AT24C02A之间接口电路的设计方法,包括接口电路的寄存器定义、逻辑功能模块设计和驱动程序的编写三个方而的内容,利用嵌入式逻辑分析仪(SigalTap Ⅱ Logic Analyzer)来分析接口信号时序,分析结果表,本接口所产生的读写时序满足I2C的通信协议要求,验证了设计的正确性。

1 AT24C02A芯片简介

AT24C02A芯片,是由ATMEL公司生产的基于I2C总线型的串行电可擦除的可编程存储器(EEPROM),内部含有2Kbit的存储单元,是通过二根线(SDL与SCL)与外部I2C控制器交换数据。

AT24C02A芯片的主要特性如下:

低电压和标准电压 *** 作

-2.7(VCC=2.7V至5.5V)

-1.8(VCC=1.8V至5.5V)

片内存储容量为256×8 bit(2K)

2线串行接口

施密特触发器,过滤输入的噪声抑制

双向数据传输协议

100 kHz(1.8V、2.5V、2.7V)和400 kHz(5V)兼容性

写保护引脚的硬件数据保护。

2 I2C通信协议

2.1 I2C通信协议简介

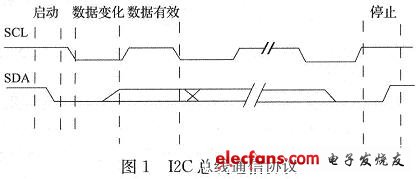

在数据传送过程中,必须确认数据传送的开始和结束信号(也称启动和停止信号)。当时钟线SCL为高电平时,数据线SDA由高电平跳变为低电平则定义为"开始"信号;当SCL为高电平时,SDA由低电平跳变为高电平则定义为"结束"信号。开始和结束信号都由主器件产生。在开始信号以后, 总线即被认为处于忙状态;在结束信号以后的一段时间内,总线被认为是空闲状态。

在I2C总线开始信号后,依次送出器件地址和数据,I2C总线上每次传送的数据字节数不限,但每一个字节必须为8位,而且每个传送的字节后面必须跟一个认可位(第9位),也叫应答位(ACK)。从器件的响应信号结束后,SDA线返回高电平,进入下一个传送周期。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)