AVR下载电路的设计

一般来说,AVR的编程方式有:

(1)串行编程,ISP编程

(2)高压/并行编程

(3)JTAG编程

(4)IAP编程

一般情况,系统板都需要设计下载线路,对AVR进行编程。目前的AVR芯片基本上都具备ISP接口,可通过ISP接口进行编程。所以,最常见的是,在系统板上留ISP接口。

那么什么是ISP呢?

ISP是In System Program的缩写,意思是在系统编程,亦即是在线编程。它一共使用了两条电源线:VCC、GND,三条信号线:SCK、MOSI、MISO,以及复位线:RESET。由于仅仅使用了几条数据线,所以我们亦常将其称为串行编程。

值得注意的是:

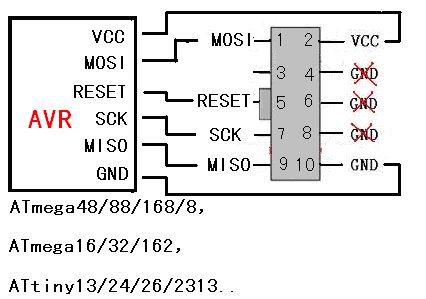

大部分AVRMCU的ISP数据端口亦为 SCK、MOSI、MISO引脚(如TIny13/24/2313,mega48/88/168/8,mega16/32/162等),如下:

[调试器] [目标MCU]

VCC -------- VCC

GND -------- GND

RESET -------- RESET

SCK -------- SCK

MOSI -------- MOSI

MISO -------- MISO

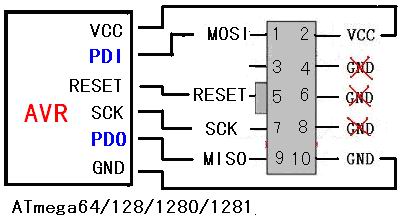

少部分AVRMCU的ISP数据端口则不是使用这些接口,而是:SCK、PDI、PDO引脚(如atmega64/128),如下:

[调试器] [目标MCU]

VCC -------- VCC

GND -------- GND

RESET -------- RESET

SCK -------- SCK

MOSI -------- PDI

MISO -------- PDO

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)