随着社会的发展,科学技术也在不断的进步。特别是计算机产业,可以说是日新月异,移位寄存器作为计算机的一个重要部件,从先前的只能做简单的左移或右移功能的寄存器到现在广泛应用的具有寄存代码、实现数据的串行-并行转换、数据运算和数据处理功能的移位寄存器。移位寄存器正在向着功能强,体积小,重量轻等方向不断发展

近年来,集成电路和计算机应用得到了高速发展,现代电子设计技术已迈入一个崭新的阶段,具体表现在:

(1)电子器件及其技术的发展将更多地趋向于为EDA服务;

(2)硬件电路与软件设计过程已高度渗透;

(3)电子设计技术将归结为更加标准、规范的EDA工具和硬件描述语言HDL的运用;

(4)数字系统的芯片化实现手段已成主流。

因此利用计算机和大规模复杂可编程逻辑器件进行现代电子系统设计已成为电子工程类技术人员必不可少的基本技能之一。

随着集成电路集成度的不断增加和工作速度的提高, 功耗急剧增加。 早在 7 年前, A lpha 处理器21164 的功耗已高达 50 W. 这给集成电路的散热、封装和便携设备的使用等都带来极大的困难。 因此,如何降低功耗成为设计集成电路时要考虑的一个重要问题。

在 CM O S 电路的功耗中决定性的一项来自于电路中对给定结点的充放电与此相应的功耗可由下式表示:

P = 0. 5CL·V2DD·f CL K·E SW ,

式中, CL 为该结点的物理电容, V DD 为电源电压,f CL K为时钟频率, E SW (称为开关活动性) 是每个时钟周期 1öf CL K中的平均输出跳变数

在一个系统中时序电路常是功耗的主要贡献者, 因为时序电路的输入信号之一就是时钟, 而它正是唯一的一直在跳变的信号。 此外, 时钟信号的负荷总是最高的。 为分布时钟以及控制住时钟偏移, 就需要构建一个含有时钟缓冲器的遍布系统的时钟网络(通常称为时钟树)。 所有这些均增加了时钟网络的结点电容的总和。 近年来的研究表明, 在数字计算机中时钟信号消耗的功耗占了系统功耗的很大比例(15%~ 45% )。 因此, 通过减少时钟功耗将可以大幅度降低电路的总功耗。

在对触发器的内部结构的分析中发现时钟信号有一半跳变是冗余的, 仅有另一半跳变才引起触发器的状态变化。 因此, 当前国际上对一种新型的双边沿触发器提出了研究。 所谓双边沿触发器是指对时钟上下跳变敏感的一种新型触发器。 使用该类触发器, 时钟信号的频率可以降低一半就能保持原来的工作速度, 从而使得对双边沿触发器的研究成为低功耗设计的一个研究热点。

注意到触发器是存储单个数字信号的存储单元, 而用触发器串接而成的移位寄存器可以认为是一种存储多位数字信号的存储元件。 因此对双边沿触发器的研究应可推广到对移位寄存器的研究中来。 本文将从双边沿触发器的设计思想出发对双边沿移位寄存器的设计思想、工作原理、低功耗特点及应用等方面展开深入研究, 以达成对该一新型低功耗器件的研究完整性

双边沿移位寄存器的设计锁存器(latch) 是构成触发器的基本单元。 锁存器的输入时钟信号 clk 用于将锁存器置于存贮状态或输入状态。 若用D、Q 和Q ′分别来表示锁存器的输入信号、现态及次态, 则高电平输入与低电平输入等两种锁存器的状态方程可表示如下:

Q ′= D ·clk+ Q ·clk , (1)

Q ′= D ·clk+ Q ·clk.,(2)

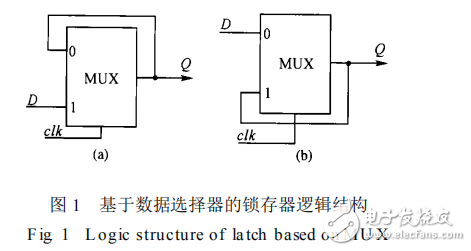

式(1) 表示锁存器在 clk = 1 时输入数据, clk = 0 时存贮数据; 而相应式(2) 为 clk = 0 时输入数据, clk= 1 时存贮数据。 图 1 (a)、(b) 分别示出了根据式(1)、(2) 利用数据选择器M U X 实现的时钟高电平时输入与低电平时输入的D 型锁存器逻辑结构

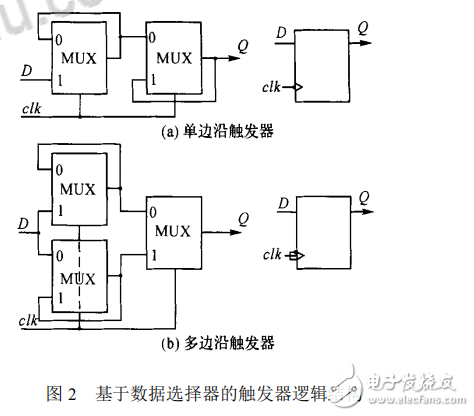

以图 1 (a) 所示的时钟高电平时输入的D 型锁存器为例, 它的工作特点为在 clk = 0 时输入信号无法影响锁存器的存贮状态, 而当 clk = 1 时, 输入信号就能影响锁存器的存贮状态。 这样, 在 clk = 1期间输入信号的多次变化将会导致锁存器发生多次状态转换。 为了实现一次状态转换, 可以要求它的输入信号在 clk = 1 时保持不变。 这一要求暗示了该锁存器的输入信号在 clk = 1 时应处于一种存贮状态, 因此也就需要另外一个反相控制的锁存器, 由此便导出了传统的主从触发结构。 图 2 (a) 即为用图 1(a)、(b) 中两种用数据选择器M U X 组成的锁存器串联而构成的单边沿主从触发器。 其中前级D 型锁存器为主锁存器, 后级D 型锁存器为从锁存器。 当clk = 1 时主锁存器处于输入状态, 而从锁存器处于存贮状态; 当 clk = 0 时主锁存器处于存贮状态, 而从锁存器处于输入状态,Q 转换为Q ′, 即该主从触发器仅在 clk 下跳时进行状态转换, 因此称为单边沿触发器(SETFF)。

一次状态转换的要求也可以从触发器的输出来考虑。 只要选择处于输入状态的锁存器与输出隔离,则该锁存器即使在输入状态下发生多次状态转换也不会影响输出状态。 这暗示了可以把串联的主从触发器改成并联的形式。 两个锁存器在时钟 clk 的作用下交替处于输入状态及存贮状态, 而最后可以用另一个数据选择器M U X 使二者中处于存贮状态的锁存器接通输出端, 如图 2 (b) 所示。 这样, 该触发器在 clk = 0、1 时都能够接收输入信号, 触发器的状态在时钟脉冲的上升沿和下降沿均可以改变, 从而实现了时钟信号的双边沿触发, 图 2 (b) 中的图形符号已在时钟输入端标志了这一特性

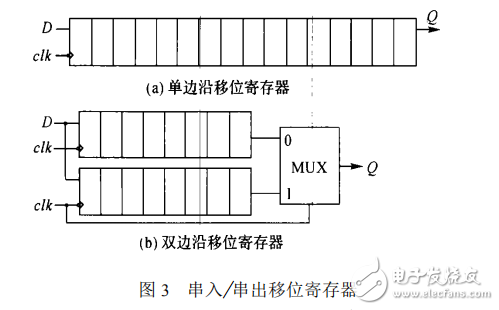

借鉴以上双边沿触发器的设计思想, 可以设计出双边沿移位寄存器。 下面以设计 16 位的移位寄存器为例进行讨论。 传统的移位寄存器设计以 16 个单边沿触发器串行级联构成, 如图 3 (a) 所示。 该移位寄存器要存储或者输出 162b it 的数据需要有 16 个时钟周期, 在此期间各个触发器均要受到 32 个时钟跳变。 如果将 16 个单边沿触发器分成两组, 每组由8 个反相触发的单边沿触发器串行级联构成单边沿移位寄存器, 再将两组触发器并联就构成了双边沿移位寄存器。 两组触发器在时钟的作用下交替处于输入状态及存储状态, 而最后可以用一个数据选择器M U X 使处于存储状态的触发器组接通输出端,如图 3 (b) 所示。 这样, 162b it 数据依次在一个时钟周期内分别由上下二组触发器轮流接收、存储并输出到移位寄存器的输出端, 在此期间每个触发器只接收到 16 次时钟信号的触发 (8 个时钟周期)。 因此, 如果保持时钟频率不变, 则移位寄存器处理的数据流量在能耗不变的前提下增加近 1 倍; 另外, 如果时钟频率降低一半, 则能在保持不变的数据流量的同时降低移位寄存器的功耗

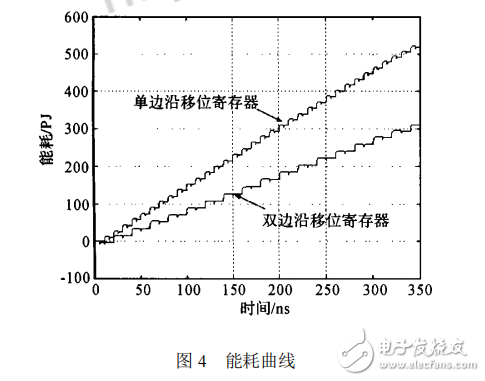

图 4 所示是在相同的数据流量的情况下单边沿移位寄存器和双边沿移位寄存器的能耗曲线。 由图可知, 双边沿移位寄存器比单边沿移位寄存器的功耗降低了 38. 5%. 可以发现, 虽然双边沿移位寄存器比单边沿移位寄存器增加了一个M U X, 但是由于开关频率减半所导致的功耗降低仍是主要的。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)