大小核(big.LITTLE)芯片设计架构正快速崛起。在ARM全力推广下,已有不少移动处理器开发商推出采用big.LITTLE架构的新方案,期透过让大小核心分别处理最适合的运算任务,达到兼顾最佳效能与节能效果的目的,以获得更多移动装置制造商青睐。

近年移动领域出现重大变革,智慧型手机已成为消费者联网生活的主要工具,然而,这其中涉及各种高效能运算任务如高速网页浏览、导航与游戏,以及语音通话、社群网路和电子邮件服务等效能需求较低的“持续运作,永远连线”后台任务。

与此同时,平板装置也正重新定义运算平台,这些创新设计转变均为消费者打造与内容互动的全新方式,将原本只限于网路共享装置(Tethered Device)的功能导入移动领域,创造出真正的智慧型新世代运算。

因应电子装置的快速变革,未来半导体向来遵循的摩尔定律(Moore‘s Law)又将如何往下发展?过去,预测芯片的效能每隔18个月就会倍增,而现今电晶体的数量已从数千增加到数十亿个,但若仔细观察单一处理器,就会发现整体的效能几乎呈现停滞不前的情况,这是因为系统能消耗的电量已达到高峰。

克服芯片效能与功耗挑战 big.LITTLE设计架构崭露头角

对于未来任何一种处理器,处理速度都将受限于散热问题而无法大幅跃进。任何装置一旦达到热障(Thermal Barrier)就会开始融化,如果是移动电话,便会使装置温度上升造成使用者不适。除物理层面的散热问题外,能源效率也会变得相当差,若调校处理器实作使其速度加快,则所需耗能便会倍数增长,而为增加最后这一丁点的效能,后续导热设计的成本真的很高。

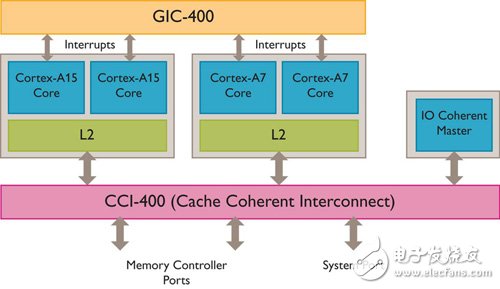

在过去,处理器核心面积倍增代表速度倍增,但是现在面积倍增,速度却只增加几个百分点,因此复杂度并不代表有效率,这就是单一核心系统有所限制的原因之一。如果无法加快单一核心速度,就必须增加独立核心的数量,这也有助于每个核心去应对其被分配到的任务需求,有鉴于此,ARM遂于2012年提出big.LITTLE处理器架构(图1)。

图1 big.LITTLE系统结构示意图

big.LITTLE 主要目的在于解决IC设计业界眼前最大挑战,也就是同时提升芯片效能,并延长装置续航力,以延伸消费者“持续运作,永远连线”的移动体验。该技术之所以能达成上述目标,系结合一个大(big)的高效能处理器核心与一个小(LITTLE)的低功耗处理器核心,然后根据效能需求,以无缝连接方式选择合适的处理器。更重要的是,这种动态分配任务的动作,对于上层应用软体或中介软体在处理器上的执行丝毫没有任何影响。

目前已应用于市面上移动装置的big.LITTLE设计,结合高效能Cortex-A15多处理器丛集(Cluster)与具有节能特色的Cortex-A7多处理器丛集。这些处理器在架构上百分之百相容,且均支援40位元实体地址扩展LPAE、虚拟化扩充及NEON、VFP之类的运作单元,无须另外调整即可让针对其中一种处理器类型所编译的软体应用程式,顺利于另一款处理器上运作。

因应任务需求 处理器核心无缝切换

两种丛集的中央处理器,还可透过CoreLink GIC-400之类的共用中断控制器互传讯号。其中,系统包含big.LITTLE切换和big.LITTLE MP(MulTIple-Processor)两种执行模式,由于同一应用程式可采用Cortex-A7或Cortex-A15而毋须调整,因此可将应用程式的任务随机对应到正确的处理器上。

切换模式是让不同处理器类型在切换时能进行软体内容的撷取与回覆。以CPU切换来说,丛集中每个CPU在另一个丛集中都有对应的CPU,而软体内容则以CPU为单位,随机在不同的丛集间切换;如果丛集中没有正在运转的CPU,便可关闭整个丛集及相关的L2快取。

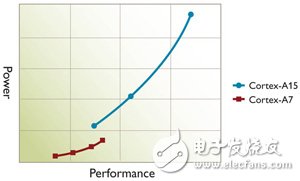

同时,此模式也是动态电压频率调整(DVFS)等能源/效能管理技术的延伸。切换动作类似DVFS *** 作点的转换,由于处理器上DVFS曲线的 *** 作点,会随负载变化不同而来回变动,当既有的处理器(或丛集)已达到最高 *** 作点,而软体堆叠仍需更高效能,处理器切换动作就会发生,改由另一个处理器执行工作,这个处理器的 *** 作点也会随着负载变化不同而来回变动(图2)。当效能需求不再,可换回之前的处理器(或丛集)。

图2 big.LITTLE切换模式DVFS曲线图

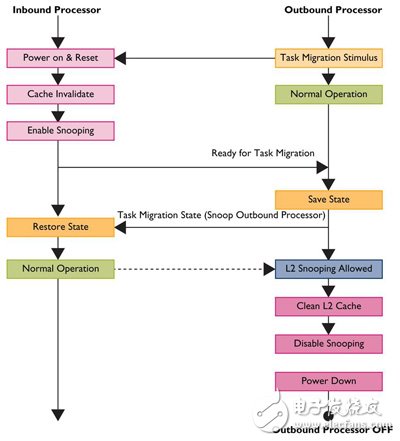

显而易见,一致性是达到加速切换所需时间的关键所在,因为它能让已经储存在离埠处理器(Outbound Processor)的状态,在入埠处理器(Inbound Processor)上窥探与回覆,而不必透过主记忆体的存取。

此外,由于离埠处理器的L2有快取一致性的功能,当任务切换时,可以透过窥探资料值的方式,改善入埠处理器的快取暖机时间,此时L2高速缓存仍然可以维持供电状态;不过,因为离埠处理器的L2快取无法提供新资料的快取配置,最后还是必须清除并关闭电源以节省耗电(图3)。

图3 big.LITTLE运算任务切换流程图

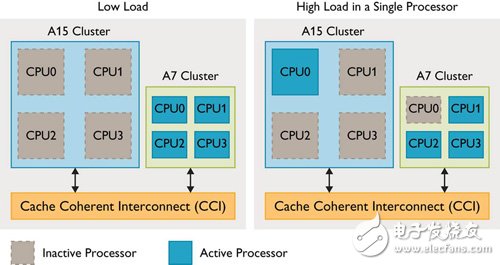

由于LITTLE处理器丛集中,每个处理器都将对应一个big丛集的处理器,因此CPU乃成对配置(Cortex-A15及Cortex-A7处理器上都有 CPU0,Cortex-A15及Cortex-A7处理器上都有CPU1,以此类推),不论何时每个配对中只有一个处理器可运转;而系统则会主动侦测各处理器负载,在高负载时将内容执行移到大核心(图4)。当负载从离埠核心移到入埠核心,便会关闭其中一个核心,这种模式让big与LITTLE核心组合能随时运转。

图4 big.LITTLE系统CPU切换示意图

[@B]big.LITTLE MP支援非对称丛集运作[@C] big.LITTLE MP支援非对称丛集运作

至于big.LITTLE MP模式则进一步将软体堆叠分配到两个丛集中各个处理器,如此一来,所有CPU皆可同时运作,将系统效能提升到最高点。

由于big.LITTLE系统可经由CCI-400达到高速缓存的一致性,因此有另一种模式能让Cortex-A15及Cortex-A7处理器同时运作并同步执行程式码,称为big.LITTLE MP,基本上可看作一种异质性多工处理模型。这是big.LITTLE系统最先进且最具d性的模式,能跨越两个丛集调整单一执行环境。

在这种使用模式下,若执行绪有上述处理效能方面的需求,便可开启Cortex-A15处理器核心并同时透过Cortex-A7处理器核心执行任务。如果没有这方面需求,则只须开启Cortex-A7处理器,在实际应用上,不同丛集的处理器核心不一定一致,而big.LITTLE MP比较容易支援非对称的丛集。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)