电子发烧友网核心提示:本文将为软件工程师揭开FPGA 的神秘面纱,主要介绍了如何为 FPGA嵌入式处理器开发软件的一些实用技巧。

随着产品设计复杂性的增加,需要使用集成组件(如特定于应用的标准产品——ASSP)来满足设计上的要求。几年前,工程师会针对处理器、存储器和外设选择单独的组件,然后通过分立逻辑器件将这些元素拼合到一起。后来,他们会搜索ASSP处理系统目录,试图找出最相称的组合,以满足系统要求。当他们需要其他逻辑或外设时,通常会将某个FPGA与某个ASSP配对来完成解决方案。的确,调查表明 FPGA在目前全部嵌入式系统中的使用比例占50%?70%。

在过去的几年中,FPGA的尺寸有了增加,在单个器件中提供了足够的空间来容纳完整的处理器和逻辑系统。现在,软件工程师需要为FPGA内部的处理器开发和调试代码。在有些情况下,他们害怕这么做。不过,通过掌握FPGA基础知识并了解如何创建和调试用于FPGA嵌入式处理器的代码可以让他们坦然面对。

FPGA是什么?

现场可编程门阵列(field-programmable gate array,FPGA)是一种集成电路,其中包含的逻辑可以在制造后进行配置和连接(即“现场模式”)。在这方面,过去工程师会从产品目录中购买各种逻辑 器件,然后通过印刷电路板上的连接将它们组装成一个逻辑设计,而现在的硬件设计人员可以在单个器件中实施完整的设计。形式最简单的FGPA中包括:

● 由与、或、非及其他许多逻辑函数组成的可配置逻辑块

● 使逻辑块可以连接到一起的可配置互连功能

利用这些元素,用户可以创建任意逻辑设计。

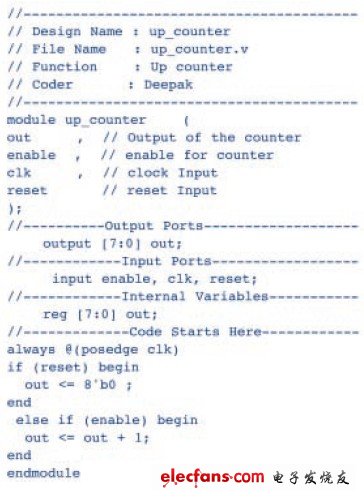

硬件工程师通常用HDL(一般是Verilog或VHDL)编写代码,然后将设计汇编到一个对象文件中,该文件可加载到器件中供执行。在表面上,HDL程序可能看起来很像C语言之类的高级语言。例如,用下面以Verilog编写的8位计数器的实现为例。其中可以看到许多目前的高级语言中的构造:

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)