现今的FPGA设计大多采用时序逻辑,需要时钟网络才能工作,通常情况下,时钟通过外部晶体振荡器产生。虽然大多数情况下使用外部晶振是最好的选择。然而,石英晶振对温度漂移敏感、且易碎,对于一些恶劣场合,如导引头制导电路、温度骤变和高速振荡使得应尽量避免使用晶体振荡器。本文主要研究如何通过FPGA内部延迟单元构建闭合组合逻辑链产生自激振荡,从而产生时钟信号,并通过内部PLL锁相环获得倍分频时钟的方法。该方法可用于应避免使用时钟的场合下代替外部晶体振荡器使用。

实现方法

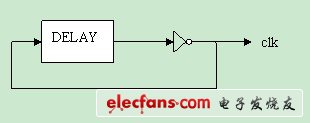

构建一个带有长延迟的闭合反相器可以获得一个自激振荡的输出信号。如图1所示。

产生自激振荡需要满足两个条件,一个是要有足够长的延迟链,另一个是要有反相器逻辑。足够长的延迟链可以通过FPGA的内建延迟逻辑或者非门链条组成,对于Altera公司的FPGA而言,内部延迟单元为LCELL,将若干LCELL串联即可组成延迟链。其Verilog HDL描述为;

wire [WIDTH:0] gcBufChain /*synthesis syn_keep=1*/;

assign gcBufChain[0] = ~gcBufChain[WIDTH];

assign dout = gcBufChain[0];

genvar j;

generate

for (j = 0; j < WIDTH; j = j + 1)

begin: dc_loop

LCELL AlteraBuf (.in(gcBufChain[j]), .out(gcBufChain[j+1]));

end

endgenerate

注意,为了防止编译器对延迟链的优化,必须在定义处注明synthesis syn_keep=1, 否则编译器会按照逻辑将其优化为直连线,无法起到延迟的效果。链的长度WIDTH需要指明,WIDTH设置过大,会导致延迟链过长,输出信号可能不稳定(Skew大),过小则会导致无法起振,根据经验,可以先取一较大值,保证起振。之后减小,获得相应的时钟频率。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)