现场可编程门阵列(Field Programmable Gate Arrays,FPGA)是一种可编程使用的信号处理器件。通过改变配置信息,用户可对其功能进行定义,以满足设计需求。通过开发,FPGA能够实现任何数字器件的功能。与传统数字电路相比,FPGA具有可编程、高集成度、高可靠性和高速等优点。

1 数字钟总体设计

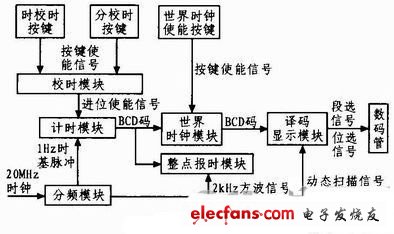

本文以FPGA平台为基础,在QuartusⅡ开发环境下设计开发多功能数字钟。数字钟实现的功能如下:

1)计时功能:进行正常的时、分、秒计时,并由6只8段数码管分别显示时、分、秒时间。

2)校时功能:当时校时按键按下时,计时器时位迅速增加,并按24小时循环;当分校时按键按下时,计时器分位迅速增加,并按60分循环。

3)整点报时功能:当计时到达59分53秒时开始报时,在59分53秒、55秒、57秒蜂鸣声频率为512 Hz;到达59分59秒为最后一声报时,蜂鸣声频率为1 kHz.

4)世界时钟功能:默认当前显示时间为北京时间(GMT+8),当按下世界时按键时,显示时间将转换为格林威治标准时(GMT)。数字钟电路的模块框图,如图1所示。

2 功能模块的工作原理及设计实现

系统主要由6大模块组成,即分频模块、计时模块、校时模块、译码显示模块、整点报时模块和世界时钟模块。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)