Virtex-6中嵌入BRAM,大大拓展了FPGA的应用范围和应用的灵活性。BRAM可被配置为单端口RAM、双端口RAM、内容地址存储器(CAM)以及FIFO等常用存储结构。

Virtex-6中的BRAM是双端口RAM,每个BRAM存储36Kbit数据,支持写和读同步 *** 作,两个端口对称且完全独立,共享存储的数据,可以改变每个端口的位宽和深度。36Kbit可配置成64K×1(和相邻36Kbit BRAM级联)、32K×1、16K×2、8K×4、4K×9、2K×18、1K×36或512×72的简单双口RAM;每个18Kbit的BRAM也可配置成16K×1、8K×2、4K×4、2K×9、1K×18或512×36的简单双口RAM。存储器内容可在配置比特流时设置。BRAM在写 *** 作过程中,它的输出数据可以编程设置,或者是保持输出数据不变,或者反映正在写入的新数据,或者是正在被覆盖的旧数据。

一、 双端口RAM和单端口RAM全双口36Kb BRAM有36Kb的存储空间和两个独立的访问口:A口和B口。类似地,每个18Kbit RAM包含一个18Kbit存储空间和2个全独立的访问口:A口和B口。结构是全对称的,数据可以写入其中的一个口或者两个,也可以从一个或者两个口读出。写 *** 作是同步的,每个口有自己单独的地址、数据输入、数据输出、时钟、时钟允许和写允许信号。读 *** 作也是同步的,并需要一个时钟边沿。

需要注意的是,当两个端口同时对同一个地址进行 *** 作的时候,由于双端口RAM内部没有专门的监控逻辑,因此需要用户自己控制两个时钟,以避免冲突。两个端口同时对同一个地址的写 *** 作虽然不会损坏该物理空间,但可能导致数据错误。

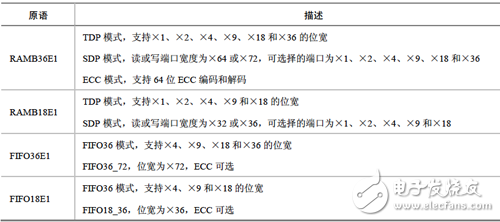

双端口RAM和单端口RAM的原语如表5-10所示,可在HDL代码中直接例化。

表5-10 单端口RAM原语

二、 FIFOVirtex-6的BRAM中的专用逻辑让用户能够轻松地实现同步或异步FIFO。这样就不必为计数器、比较器或状态标记的生成使用其他CLB逻辑。

Virtex-6中,FIFO 可配置成18Kbit 和36Kbit 存储空间,对于18Kbit 的FIFO,支持4K ×4、2K×9、1K×18 和512×36;对于36Kbit 的FIFO,支持8K×4、4K×9、2K×18、1K×36 和512×72。

三、 ECC 内置纠错当使用Virtex-6 中的RAMB36E1(SPP 模式)或者36Kbit FIFO(FIFO36E1)时,可以使能其中的ECC 纠错功能。ECC 占用72 位宽,其中64 位数据,8 位汉明码,它可以产生汉明位并纠正输出的数据错误,但不会纠正存储器内容。另外,它还可以输出错误位置的地址。

在写 *** 作过程生成八个保护位(ECCPARITY),与64 位数据一起存到存储器中。这些ECCPARITY 位在每次读 *** 作过程中用来纠正任意单位元错误或检测(但不纠正)任意双位元错误。

在读 *** 作过程中,72 位数据从存储器读出并馈入ECC 解码器。ECC 解码器生成两个输出状态(SBITERR 和DBITERR),用来指示三种可能的读 *** 作结果:无错误、已纠正单位元错误、检测到双位元错误等。在标准ECC 模式下,读 *** 作不纠正存储器阵列中的错误,仅仅将已经纠正的数据送到DO。为了改善FMAX,可以将由DO_REG 属性控制的可选寄存器用于数据输出(DO)、SBITERR 和DBITERR。

Virtex-6 中的ECC 还增加了一个新的功能,能回读当前数据输出对应的存储地址,支持修复错位的数据位或者将该地址设置成无效。

Virtex-6 BRAM 模块的详细资料请参考附带光盘上的《Virtex-6 BRAM 用户手册》。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)