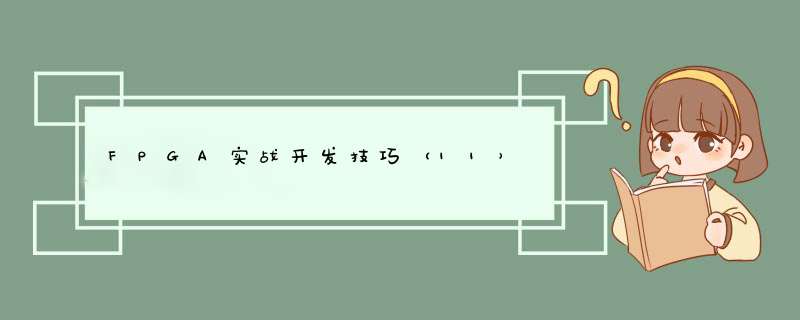

在串行模式下,需要微处理器或微控制器等外部主机通过同步串行接口将配置数据串行写入FPGA芯片,其模式选择信号M[2:0]=3’b111。典型的Spartan 3E系列FPGA单片配置电路如图5.5.11所示。DIN输入管脚的串行配置数据需要在外部时钟CCLK 信号前有足够的建立时间。其中单片FPGA 芯片构成了完整的JTAG链,仅用来测试芯片状态,以及支持JTAG 在线调试模式,与从串配置模式没有关系。外部主机通过下拉PROG_B启动配置并检测INIT_B 电平,当INIT_B 为高时,表明FPGA 做好准备,开始接收数据。此时,主机开始提供数据和时钟信号直到FPGA 配置完毕且DONE 管脚为高,或者INIT_B 变低表明发生配置错误才停止。整个过程需要比配置文件大小更多的时钟周期,这是由于部分时钟用于时序建立,特别当FPGA 被配置为等待DCM锁存其时钟输入。

图5-32 FPGA从串配置电路示意图

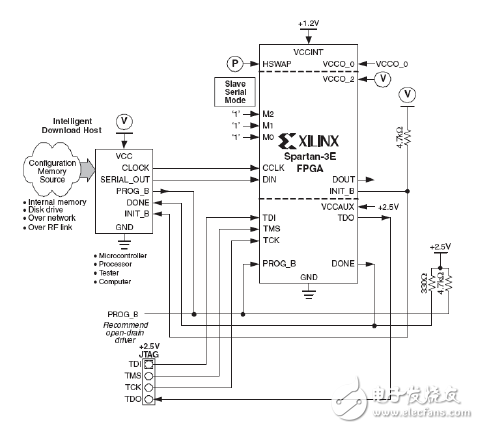

此外,从串配置模式也可配置多片FPGA芯片,典型的两片Spartan 3E系列FPGA的从串配置电路如图5-33所示。所有芯片的CCLK信号都有主控设备提供,靠近主控设备的FPGA要充当桥梁的作用,将配置数据转发到第二个FPGA芯片。可以看到采用从串配置的好处主要在于节省电路板面积,并使得系统具备更大的灵活性。

图5-33 多片FPGA从串模式配置电路

5.5.5 JTAG配置模式1.JTAG配置电路

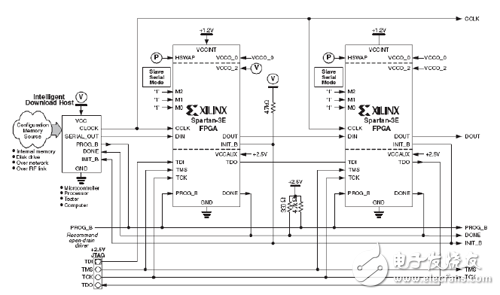

赛灵思公司的FPGA芯片具有IEEE 1149.1/1532协议所规定的JTAG接口,只要FPGA上电,不论模式选择管脚M[2:0] 的电平,都可用采用该配置模式。但是将模式配置管脚设置为JTAG模式,即M[2:0]=3’b101时,FPGA芯片上电后或者PROG_B管脚有低脉冲出现后,只能通过JTAG模式配置。JTAG模式不需要额外的掉电非易失存储器,因此通过其配置的比特文件在FPGA断电后即丢失,每次上电后都需要重新配置。由于JTAG模式已更改,配置效率高,是项目研发阶段必不可少的配置模式。典型的Spartan 3E系列芯片的JTAG配置电路如图5-34所示。

图5-34 JTAG模式配置电路示意图

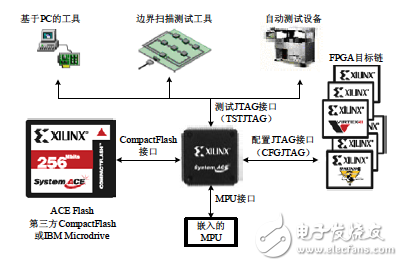

5.5.6 System ACE配置方案随着FPGA成为系统级解决方案的核心,大型、复杂设备常需要多片大规模的FPGA。如果使用PROM进行配置,需要很大的PCB面积和高昂的成本,因此很多情况下都利用微处理由从模式配置FPGA芯片,但该配置方案容易出现总线竞争且延长了系统启动时间。为了解决大规模FPGA的配置问题,赛灵思公司推出了系统级的System ACE(Advanced ConfiguraTIon Environment) 解决方案。

System ACE可在一个系统内,甚至在多个板上,对赛灵思的所有FPGA进行配置,使用Flash存储卡或微硬盘保存配置数据,通过System ACE控制器把数据配置到FPGA中。目前,System ACE有System ACE

CF(Compact Flash)、System ACE SC(Soft Controller) 以及System ACE MPM(MuTI-Package Module) 三种。读者需要注意的是:System ACE SC/MPM 是和System ACE CF 独立的解决方案。典型的ACE 接口以及系统组成如图5-35 所示。

图5-35 典型的ACE接口以及系统组成示意图

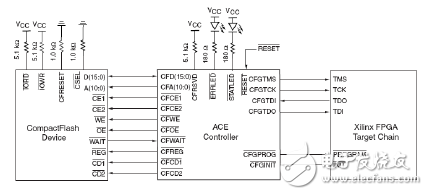

1.System ACE CF解决方案System ACE CF的核心是System ACE CF存储设备和System ACE控制器芯片。System ACE CF存储设备包括赛灵思的ACE Flash卡或其它厂家的Compact Flash卡以及IBM的微硬盘。Compact Flash卡的容量为32MB~4GB,微硬盘的容量为2GB~6GB,至少可配置数百片FPGA芯片。

System ACE CF控制器提供了存储单元和FPGA器件之间的接口,PC和存储器的标准JTAG接口。控制器芯片默认的配置模式也是通过边界扫描的方式将数据配置到FPGA 链中,同样可由边界扫描链的测试和编程接口来辅助进行系统原形的调试,其主要特点有:

- 支持赛灵思所有FPGA芯片的配置;

- 以最小的PC板空间实现多达8Gb的配置 ;

- 包括高达152Mbps的配置速率;

- 利用带有嵌入式处理器核的FPGA进行系统调节;

- 管理多个比特流( 全部或部分),并按需要对其进行激活;

- 包含处理器核初始化;

- 软件存储加密;

- 可移动存储器件;

- 降低了定制配置系统的成本,支持大多数 CompactFlash卡,包括Microdrive单元;包含内置式微处理器接口,可以直接调整FPGA配置;释放设计资源。

图5-36 System ACE CF配置电路示意图

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)