摘要:基于Xilinx 的Virtex-II Pro 开发板实现了双核嵌入式系统构建,具有共享存储器及共享串口输出的特性。主要给出了双核系统的构建方法及原理,共享串口的输出验证了双核系统的可行性。

随着信息技术的逐渐发展,传统的嵌入式单核系统已经不能适应高性能的计算要求,基于FPGA 的双核系统架构也逐渐发展起来。Xilinx 公司设计的Virtex-II Pro 开发板有较高的硬件配置,由Digilent 公司制造,有高达30,816 个逻辑单元的XC2VP30 FPGA 芯片,主芯片XC2VP30 上内置两个硬核PowerPC405,136个18 位的乘法器、2 448 Kbit 的Block RAM,在各大学中使用广泛。但Xilinx 公司的系列开发工具并不支持在此开发板上构建双核,Xilinx 公司也没有提供如何利用此双核的技术文档,并且Virtex-II Pro 开发板只具有一个串口输出,调试不便,所以国内的多数大学实验室都是进行的单核PowerPC405 的应用开发,没有利用到其有两个硬核的优势,造成资源闲置。

为了充分利用Virtex-II Pro 开发板的双核资源,提出了一种构建双核的方法,步骤简洁明了,下载调试方便,共享串口的输出结果验证了此双核系统的可行性,且对Virtex II Pro及Virtex4 系列面临同样问题的开发板也具有指导意义。

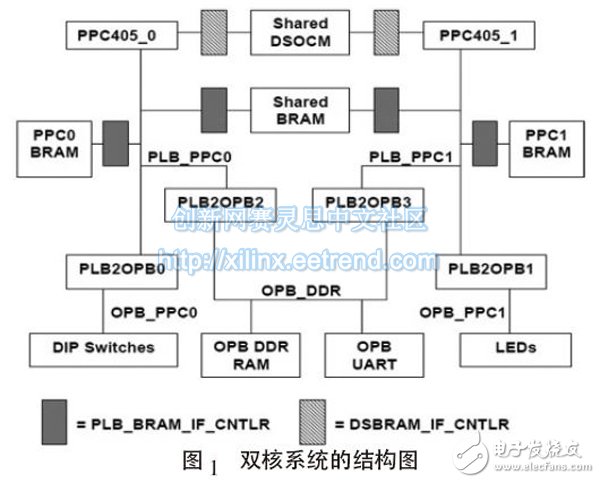

1 硬件系统构建开发工具为EDK9.1i02,硬件结构如图1 所示。

硬件体系利用了PPC_0 和PPC_1 两个处理器,它们共享了一部分外设,共享的外设需要设置共享通道。各处理器也可独占部分外设, PPC_0 通过总线桥控制外设DIP Swiches,PPC_1 控制外设LED_4Bits,可以验证各处理器的工作状态,为了保存程序,为两个处理器分别设置了独占的Boot BRAM及中断控制器和复位控制器。2 个PowerPC 共享JTAG,都能通过串口进行输出。

系统设计流程如下:

(1) 利用XPS 生成单核系统系统参数设置如下:

①System clock:频率100 M,无缓存。

②RS232:波特率115200,8 位,无中断。

③DDRAM:片内存储器512MB,无中断。

④LEDs_4 Bit:无中断。

配置好后的总线与端口如图2 所示。

(2) 添加PPC405_1 及相关设置

1) PPC405_1 的设置

添加新的IP 核PPC405,则PPC405_1 已经随PPC405_0一起添加到了工程中,只不过还没有连上线而已。点击Businterface,把DPLB 和IPLB 分别连到PLB 总线上。然后点击-Ports,配置PPC405_1 的端口, (默认情况下,有PLBCLK,BRAMDSOCMCLK,BRAMISOCMCLK 这三个端口看不到,需要点击ConnecTIon Filters 才会看到) 增加一个Reset 的IP 模块,选择Reset Control->Processor System Reset Module,会生产一个proc_sys_reset_0 模块。配置IP 属性中External ResetAcTIve High 的值为0。为了方便验证两个核是否正常工作,用UART 为PPC405_0 显示运行信息,用LED 为PPC405_1 显示运行信息,所以增加一个Opb_gpio 核,属性为位宽4 bit,设置Channel 1 为Bi-direcTIonal, Channel 1 的Input Only 设置为FALSE。

2) jtagppc_cntlr 核的配置

BEGIN jtagppc_cntlr

PARAMETER INSTANCE = jtagppc_0

PARAMETER HW_VER = 2.00.a

BUS_INTERFACE JTAGPPC0 = jtagppc_0_0

BUS_INTERFACE JTAGPPC1 = jtagppc_0_1

END

3) 共享BRAM 核的配置

BEGIN bram_block

PARAMETER INSTANCE = share_bram

PARAMETER HW_VER = 1.00.a

BUS_INTERFACE PORTB=share_bram_if_cntlr_1_PORTA

BUS_INTERFACE PORTA = share_bram_if_cntlr_0_

PORTA

END

(3) 配置地址

给外设和OCM 分配地址,对于powerpc,ISOCM 必须落在地址的最高端,DSOCM 可以随意。

(1) 配置软件平台

为PPC405_1 添加应用程序是最关键的一步,所以要分别为PPC405_0 和PPC405_1 设置编译选项,也就是修改Linkerscript(.ld 文件),一种可行的方法是:把启动代码和数据分别放在两个核独立的Isbram_if_cntrl 和dsbram_if_ctrl 中,而把stack 和heap 放在公共的bram 中,如Plb_bram_if_ctrl 中。

(2) 添加应用工程

添加工程ppc0_test_share 和ppc1_test_share,分别Mark to iniTIalize BRAM,并将软件工程指定给各自的处理器,所有程序段则放入各自的私有BRAM 中,更新Bitstream 以生成相应的全局比特流文件。

为两个核设置software Platform settings,其输入输出设备都配成UART,,然后生成库和BSP,编译应用程序,更新bitsream,最后下载bitsream 到FPGA,输出到超级终端则能验证双核配置的正确与否。

2.2 互锁程序的编写

互锁程序是在xilinx 自带的测试程序基础上修改而成,主要的修改部分在于添加识别处理器状态的程序,作用在于保证两个处理器不会互相干扰,其中定义了lwarx.PPC and stwcx.PPC 两个声明,并为了让gcc 编译器顺利编译,编写如下代码:

#define lwarx (adr) ({unsigned int rval; \

__asm__ __volatile__ (\

" lwarx %0,0,%1\n" \

: " =r" (rval) :" r" (adr) \

) ;\

rval;\

})

#define stwcx (adr,val) __asm__ __volatile__ (\

" stwcx. %0,0,%1\n" \

: : " r" (val) ," r" (adr) \

)

互锁程序通过变量Pr_Lock 的值来表示串口占用情况,0 表示空闲,1 表示PPC_0 占用,2 表示PPC_1 占用,代码段如下:

volatile int* Pr_Lock = PR_LOCK_ADDR;

void PRLOCK ()

/* PRLOCK implements a TEST & TEST & SET using the

PPC stwcx and lwarx instructions*/

{

while (1)

{

while (*Pr_Lock ! = 0) ; //等待释放

if (lwarx (Pr_Lock) ! = 0) continue; //锁存

stwcx (Pr_Lock,MY_LOCK_VAL) ;

if (*Pr_Lock == MY_LOCK_VAL)

{

sync; // 返回

return;

}

else continue; // 重试

}}

void PRUNLOCK ()

{

// 等待清空

while ( XUartLite_mIsTransmitEmpty

(XPAR_RS232_UART_1_BASEADDR) == XFALSE) ;

sync;

*Pr_Lock = 0;

return;

}

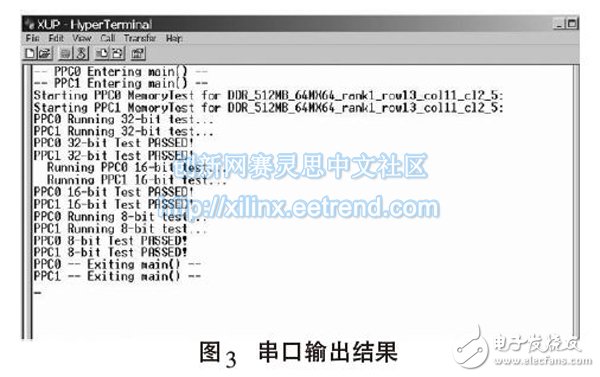

配置好超级终端,连接好电缆,下载线,将比特流文件输出到开发板上。通过共享的串口输出,两个处理器的运行状态均可显示。输出结果如图3 所示。

实现了在FPGA 开发板上的双核系统构建,充分利用了系统资源,能通过互锁程序合理控制共享的外设,并能共用一个串口进行输出,克服了调试不便的难题。设计方法简单易行,运行结果证明了可靠行,在开发板厂商没有提供相关资料的情况下,该系统为基于FPGA 的双核嵌入式系统设计提供了参考价值。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)