摘 要:针对目前水下三维声纳实时成像系统前端信号通道多、波束形成计算量大的问题,提出一种基于现场可编程门阵列(FPGA)的水下三维场景实时成像系统。采用FPGA 阵列控制多路信号同步采样,优化波束形成算法对海量数据进行并行处理,同时利用嵌入式处理器PowerPC 控制系统,最终由主控PC 完成三维图像实时显示。实验结果表明,该系统能够在水下200 m 的范围内实现分辨率为2 cm 的三维成像,三维图像刷新率可达20 帧/秒。

1 概述近年来,随着人们对海洋资源的不断需求与开发,水下探测技术得到了飞速发展。人们对海洋的主要探测手段是声波,即声纳技术。因此,利用声纳进行水下探测成为了当今海洋研究的重点课题。然而,大部分声纳系统都是通过声波来判断有无声纳目标,以及目标的方位和距离。目前,国内外在海底三维声纳成像技术方面已经取得了一定的成果[1]。例如:美国RESoN 公司开发的新一代数字声纳SeaBat8125,欧洲共同体和挪威共同开发的Echoscope系列三维声纳,美国的海洋工业公司开发的双频识别声纳以及美国的Farsounder 公司开发的三维前视声纳[2-3]。我国三维成像声纳也得到一定的发展,中科院声学所、715 所和哈尔滨工程大学等单位等都研制了三维声纳成像系统的试验样机并发表了相关论文[4]。但这些声纳成像技术大多基于二维映射三维图像,或者小范围的慢速三维成像,成像效果不佳,实时性太差[5]。

本文提出基于三维声纳探测技术的水下三维场景实时成像系统,设计并实现48×48 路信号的同步采样,128×128 个空间波束形成的大规模数据处理和实时水下三维场景成像。

2 系统总体设计 2.1 系统技术特点目前,实时高分辨率的三维声纳系统面临2 个问题[6]:

(1)大量前端信号通道的硬件成本昂贵;(2)进行波束形成算法所需的乘累加计算量大。

首先,该系统采用了优化后的模拟退火算法[7],对二维平面上的每一个换能器分配权重系数,在最大旁瓣可以接受的条件下,部分换能器的权重系数可以分配为0,即达到对换能器稀疏化,减小系统运算量的效果[8]。最终实现系统2 304(48×48)个换能器组成的声学信号接收平面阵。

同时,该系统采用优化后的分步波束形成算法,将空间入射的声波信号进行空间分解,对相移参数进行优化,从而减小相移参数储存空间,并将声学信号接收平面阵划分成48 条线性子阵,分组并行实现分步波束形成,最终完成128×128 个波束形成[9]。

由于FPGA 具有数据位宽可配置性、多级流水线处理以及内部集成大量的数字信号处理单元(DSP Slices)等特性,因此FPGA 在声纳信号处理方面的运算效率远大于数字信号处理器(DSP)的运算效率[10]。为了做到实时的海量数据处理,该系统采用了基于FPGA 平台的系统设计,利用FPGA 阵列对数据进行并行处理,并通过阵列间的数据交互完成波束形成。

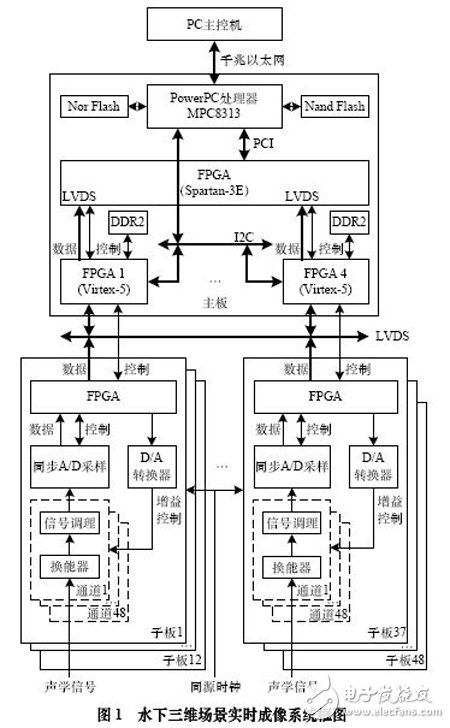

2.2 系统总体构架水下三维场景实时成像系统总体结构如图1 所示,由48 块子板、主板和主控PC 组成。子板负责完成信号采集功能,主板负责完成波束形成与数据汇总,并实现对子板的采样控制和与主控PC 通信的功能,最终在主控PC 上完成实时三维成像。其中,每块子板有48 个信号接收通道。

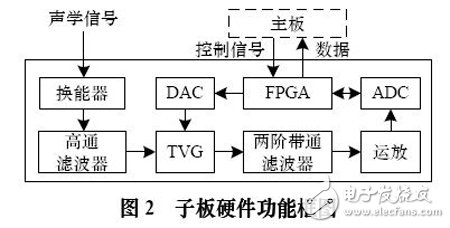

子板主要由输出放大器ADA4841、4 路功率放大器SSM2164、12 bit 串行AD 转换器ADS7886 和DA 转换器LTC2641、LTC1019、Xilinx Spartan-3E 系列FPGA XC3S1200E以及其他外围电路构成。

子板数据采集功能如图2 所示。各通道首先对从换能器接收的微弱的电信号进行调理,将信号通过一个高通滤波器滤除中低频的环境噪声后,再经过一款二阶带通滤波器,以实现当输入信号频率大于570 kHz 时使信号衰减20 dB 以上,同时保证有效的信号范围270 kHz~330 kHz(考虑水声信号的多普勒频移)衰减小于3 dB。然后在外部同源时钟驱动下,Spartan-3E 控制A/D 采样芯片对声学信号的幅度和相位信息进行同步A/D 采样和采样数据处理,并通过低压差分信号(Low-voltage DifferenTIal Signaling, LVDS)接口将数据上传主板。同时,Spartan-3E 通过串行外设接口(Serial Peripheral Interface, SPI)向D/A 转换器发送数据,经转换后输出时间增益(TIme VariaTIon of Gain, TVG)控制信号,以控制采样信号压缩比。

主板主要由1 片PowerPC 嵌入式处理器MPC8313、1 片Xilinx Spartan-3E 系列FPGA XC3S1200E 和4 片高性能Xilinx Virtex-5 系列FPGA XC5VSX95T,以及其他外围电路组成。

每块Virtex-5 通过LVDS 接口接收12 块子板上传的数据,通过高速差分对数据线彼此进行数据交互。每块Virtex-5对数据进行计算处理并完成波束形成,经2 片64 MB 外部DDR2 暂存,将波束形成结果上传至Spartan-3E 进行数据汇总。MPC8313 通过外设部件互连标准(Peripheral Component Interconnect, PCI)接口对Spartan-3E 中的数据进行读取,将波束形成汇总结果通过千兆以太网口传输给PC 主控机。同时,MPC8313 使用系统双线式串行(Inter-integrated Circuit,I2C)总线对Virtex-5 寄存器进行配置,生成D/A 驱动信号下发子板。MPC8313 外围扩展有Nor Flash 用于存储系统代码,Nand Flash 用于存储有效传感器的编号和相应的权重系数等系统相关数据。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)