1、LMK0480X 供电电路介绍

LMK0480X 系列时钟产品是 TI 近年推出的时钟抖动滤除芯片,采用了两级锁相环级联架构。第一级锁相环主要利用窄带环路滤波器,滤除参考输入(CLKin)的相位噪声和杂散,起到时钟去抖的作用,利用外部 VCXO 产生一个干净的系统参考时钟。第二级锁相环主要是利用第一级输出作为其参考时钟,生成系统所需要的各种时钟频点,同时满足系统设计所需要的相噪、抖动和杂散要求。在实际应用中,外部 VCXO 的选取,环路滤波器的设计以及各种环路参数的优化,都对最终的时钟性能有很大的影响。除这些因素外,芯片的供电设计是应用中需要考虑的另外一个重要部分,不当的设计会直接导致输出时钟不能满足系统的需求,尤其是一些对抖动和毛刺要求较高的应用场景。

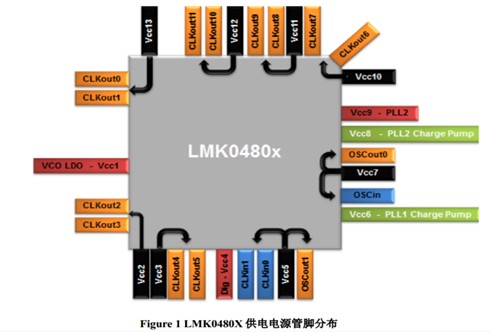

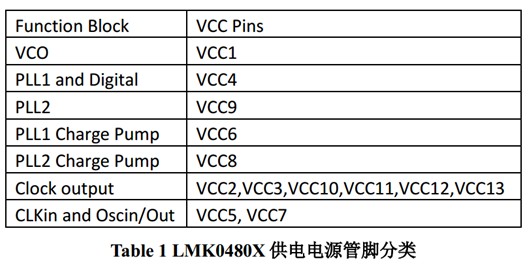

LMK0480X 芯片的供电电源管脚的分布如上图所示,大致可以分为以下几类:

本章中主要整体介绍了 LMK0480X芯片内部模块电路的供电设计。下一章节中将结合实际实验,详细介绍LMK0480X 的供电电源噪声对实际性能的影响。

2、LMK0480X 供电设计和 PSRR 性能测试

2.1 LMK0480X 供电设计原则

针对不同种类的供电管脚,对外部的供电电路的需求不同,一般需要遵循的原则如下:

• LMK048XX 所有的供电管脚内部都有一个集成的高频去耦电容,由于这个电容更加靠近芯片,可以排除封装 bonding 线的寄生电感的影响,去耦的效果比外部的高频去耦电容(《 1nF)更有效。同时外部的去耦电容容易将地平面的一些高频干扰引入到芯片的供电管脚,所以一般不建议在 LMK0480X 的所有供电管脚增加《 1nF 的去耦电容。

• VCC1,VCC4,VCC9 所负责的芯片内部电路不会产生噪声,所以这三个供电管脚可以连接在一起,共享供电电路;也不需要增加磁珠隔离管脚和总的供电电路,因为磁珠容易影响 VCO 的供电(VCC1),在输出形成鼓包。

• VCC6 和 VCC8 是给前后两级锁相环的电荷泵供电,这对芯片的最终性能至关重要,建议独立的供电支路。对于 VCC6,由于是给第一级锁相环供电,一般第一级锁相环的鉴相频率都比较低,所以供电支路的磁珠可以省去,同时也可直接把 VCC6 直接接入 VCC1/4/9 的电路。而对VCC8 而言,由于为了增加环路带宽,第二级锁相环的鉴相频率比较高(》50MHz),为了防止鉴相频率泄露到其他供电管脚,要求 VCC8 具有独立的供电支路,同时应当增加磁珠以隔离VCC8 和主供电电路的干扰。当鉴相频率较低时,可以考虑去掉这个磁珠。

• VCC5 和 VCC7 主要是给芯片的参考和 VCXO 的输入输出提供电源,同时也给 PLL2 的锁定指示电路提供电源。对于这些管脚,不需要外部的大的去耦电容和磁珠,以防止一些地平面的干扰串入电源管脚,从而影响 PLL2 的锁定指示。

• VCC2, VCC3, VCC10, VCC11, VCC12, VCC13 是给芯片的 12 路输出提供电源(一个供电管脚负责两路输出)。如果其中几路输出相同的频点时,这几路的供电可以连接到一起,共享供电支路,简化设计。由于输出频率都比较高,所以对于这几路供电管脚建议增加磁珠,以降低芯片开关噪声对于芯片整体供电的影响,同时提高通道间的隔离。同时如前面提到,由于芯片内部已经集成了高频去耦电容,所以不需要外部的去耦电容。

当输出的频率较低时(〈10MHz),或者输出单端 LVCMOS 或者高摆幅的 LVPECL 信号时,为了降低供电环路的阻抗,建议去掉磁珠或在管脚处增加一个大一点的去耦电容,提供开关电流。

• 当输出时钟类型是 LVPECL 时,应防止输出到地有电容。因为这样很容易形成到地的短路环路,不仅需要电源管脚提供很大的开关电流,同时将频率噪声引入到地平面,给系统带来了干扰。

2.2 PSRR(Power Supplier RejecTIon RaTIo)性能分析

为了表征各类不同供电管脚的电源噪声对 LMK0480X 输出噪声的影响,通常采用电源噪声抑制比 PSRR来表征锁相环芯片的抗电源噪声能力,本节通过实际测试样例评估 LMK0480X 的供电噪声抑制性能。

2.2.1 测试设置

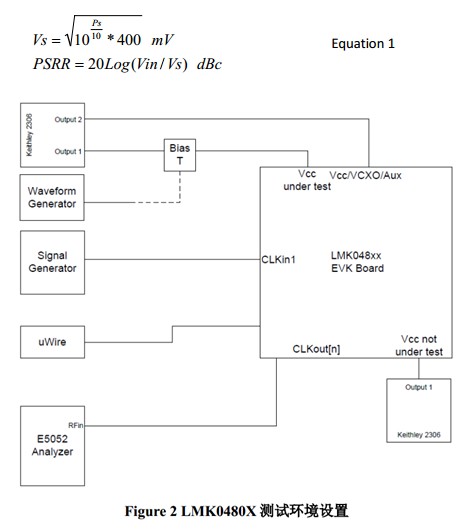

PSRR 测试基于 LMK0480X 评估板,在这些测试中,测试框图如 Figure2,设置如下:

1. 外部 VCXO 使用独立的干净电源供电,排除 VCXO 对测试结果的影响。

2. 去掉芯片外部的去耦电容和磁珠,排除这些器件对芯片 PSRR 的影响。

3. 干扰源通过信号发生器产生合路进入测试的电源管脚。干扰源的频率从 50KHz 到 2 MHz 连续扫描,测试干扰信号在环路带宽内外,对于芯片 PSRR 性能的不同影响。

4. 干扰源输入信号的摆幅固定在 Vin = 100mV;测量输出端口载波两侧的对应的干扰源带来的杂散(偏移对应的干扰源频率)的功率 Ps dBm,将 Ps 转换为电压幅度 Vs,转换公式以及 PSRR计算公式如 Equation 1 。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)