音频和视频处理、雷达、电信、驱动电机控制、虚拟现实 (VR)、增强现实 (AR) 以及最近的人工智能 (AI) 算法等应用都强烈依赖于 DPS(数字信号处理器),因为它们采用物理模拟信号的数字化形式按照特定算法在数学上对其进行 *** 作。

许多 DSP 仅支持定点数学表示并能够提供大多数科学应用所需的精度,但另一方面,浮点提供了一种更相关和更准确的方式来表示主要是模拟信号的现实世界数据. 此外,浮点支持与 DSP 代码的集成和移植,因为它们根据标准 IEEE754 的算术表示被编译器、开发和建模工具广泛使用。

“Tensilica 在 DSP 领域已经有很长时间了。我们已经为音频和语音、雷达、激光雷达和计算机视觉(包括人工智能)提供了经过验证的产品。这是 Tensilica 产品组合中的一个全新系列,也是我们第一款专为支持浮点运算而设计的 DSP”,Cadence 的 Tensilica DSP 产品管理和营销总监 Ted Chua 说。

新的 Cadence Tensilica FloaTIngPoint DSP 系列以极低的功耗为广泛的计算密集型应用提供可扩展的性能。低能耗 DSP IP 优化了功耗、性能和面积 (PPA),可为移动、汽车、消费类和超大规模计算应用节省高达 40% 的面积,并为无缝软件迁移提供简单的编程环境。

“在某些应用中,例如电机控制,浮点可以比定点系统做得更好,因为代码更小,或者因为它运行得更快,或者更准确、更有效地控制速度和扭矩”,蔡说。

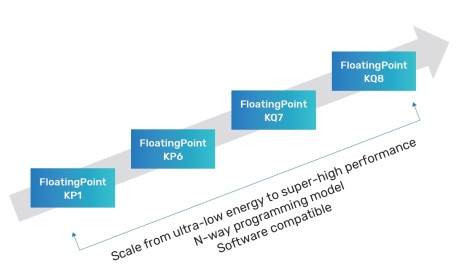

Tensilica 浮点 DSP 系列

新的浮点 DSP IP 内核系列针对 PPA 进行了优化,从小型和超低功耗扩展到非常高性能的设备,为最具挑战性的应用提供节能解决方案,包括电池供电设备、人工智能 (AI)机器学习 (ML)、电机驱动控制、传感器融合、增强现实 (AR) 和虚拟现实 (VR)。

基于 Tensilica Xtensa 32 位 RISC 微架构,新系列(图 1)包括四个内核:Tensilica FloaTIngPoint KP1 DSP、Tensilica FloaTIngPoint KP6 DSP、Tensilica FloaTIngPoint KQ7 DSP 和 Tensilica FloatingPoint KQ8 DSP。新的 DSP 不仅提供从 128 位向量宽度到 1024 位向量宽度的高可扩展性,而且还可以配置为仅启用特定应用所需的功能,从电池供电设备的节能解决方案到高-性能计算(HPC)。

图 1:Tensilica 浮点 DSP 系列

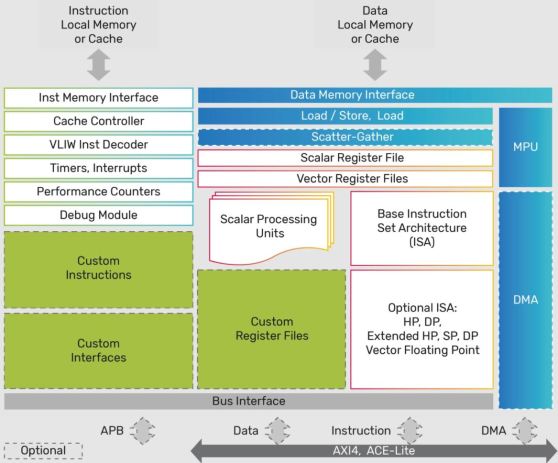

新系列 DSP 内核与现有 Tensilica DSP 的可选矢量浮点单元 (VFPU) 共享通用指令集架构 (ISA),并在 Tensilica Xtensa LX 上具有从 128 位 SIMD 到 1024 位 SIMD 的可扩展矢量宽度和 NX 平台。使用 VFPU 插件的 Tensilica 定点 DSP 的性能得到了改进,在融合乘加 (FMA) *** 作中的 *** 作吞吐量增加了 25%。使用 Tensilica 指令扩展 (TIE) 语言可以进一步增强和区分性能,这是一种 Cadence 专有的类似 Verilog 的语言,允许定义由 Xtensa 工具链自动集成和识别的自定义 *** 作。此外,与采用 VFPU 的同类定点 DSP 相比,浮点 DSP 可节省高达 40% 的面积。

图 2:Tensilica FloatingPoint KQ7 和 KQ8 框图。

如图 2 所示,可扩展的 Tensilica FloatingPoint DSP 系列为 SoC 设计人员提供了能够满足其 PPA 预算范围的设计灵活性。对于对能量敏感的应用,FloatingPoint KP1 DSP 提供了超低能耗的解决方案,适用于电池供电的应用。FloatingPoint KP6 DSP 在高性能和减少占用空间之间提供了适当的折衷,提供了出色的单位面积性能设计。对于高性能应用,FloatingPoint KQ7 和 KQ8 DSP 提供了最大系列的矢量浮点运算吞吐量。

此外,通用 ISA 架构简化了软件的可移植性和迁移。FloatingPoint DSP 还支持自定义接口,例如队列和端口,简化连接和与外部硬件模块的集成,或匹配现有第三方 IP 提供的接口。

大多数具有挑战性的应用程序都在快速发展并从云端转移到边缘。计算机视觉、物联网传感器、自动驾驶汽车和智能设备只是人工智能 (AI) 算法在边缘移动的几个例子,它们为嵌入式系统提供了增强的自主决策技能。所有这些应用都需要一系列浮点 DSP 内核,这些内核可以满足不同的市场需求、缩短上市时间,并针对功耗、性能和芯片面积进行优化,以保持产品成本竞争力。

“今天,边缘的人工智能推理主要是通过定点加速完成的。浮点 DSP 提供了以浮点格式执行 AI 推理或训练的选项,我们都知道神经网络训练是使用浮点表示完成的”,Chua 说。

如前所述,可配置性是 Tensilica FloatingPoint DSP 系列的另一个相关关键因素。Chua 评论说:“我们的 Tensilica DSP 是可配置的,这意味着设计人员可以只选择他们需要的硬件功能,而不会消耗不必要的功率。”

最有用的选项之一是分散收集功能,它允许设计人员从特定的内存位置加载数据并将其放入矢量格式。

“DSP 内部的浮点单元是一个向量机。对于未存储在连续内存位置的数据,分散收集功能允许您将分散的数据加载为一种矢量格式,从而提高整体性能”,Chua 补充道。

在与软件开发相关的方面,Tensilica FloatingPoint DSP 附带一整套软件工具,包括具有自动矢量化和指令捆绑功能的高性能 C/C++ 编译器,以支持 DSP 中的 VLIW 流水线、链接器、汇编器、调试器、分析器和图形可视化。一个有用的工具是指令集模拟器 (ISS),它允许设计人员快速模拟和评估性能。在处理大型系统或冗长的测试向量时,Tensilica TurboXim 模拟器选项声称可以实现比 ISS 快 40 到 80 倍的速度,以实现高效的软件开发和功能验证。

Tensilica Xtensa SystemC (XTSC) 和基于 C 的 Xtensa 建模协议 (XTMP) 系统建模可用于全芯片仿真。引脚级 XTSC 提供协同仿真或 SystemC 和 RTL 级卸载加速模块,用于快速、周期精确的仿真。Tensilica FloatingPoint DSP 支持所有主要的后端 EDA 流程,包括优化的 Eigen 库、NatureDSP 库、SLAM(同时定位和映射)库和数学软件库,使移植和迁移浮点软件更加容易。

“通过我们的浮点 DSP 系列,我们提供了一套软件工具,这些工具与用于 Tensilica DSP 的所有其他软件工具都是通用的。对于任何已经熟悉 Tensilica 软件工具的开发人员来说,实际上没有学习曲线,因为它是完全相同的工具”,Chua 说。

审核编辑:汤梓红

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)