首先分析Chirp函数在频域上的一般特性,提出利用FPGA的嵌入式软核NiosⅡ处理器在嵌入式 *** 作系统μC/OS-Ⅱ上实现Chirp的方法,即通过NiosⅡ处理器根据Chirp函数在频域上频率的跳变情况实时改变输出DDS(直接数字合成序列)模块的频率步进控制字的办法,控制DDS模块的频率输出,实现Chirp函数所要达到的扫频输出性的目的。通过在NiosⅡIDE编程环境中的Console窗口观察,该设计能很好地实现Chirp函数功能。

l 系统总体设计

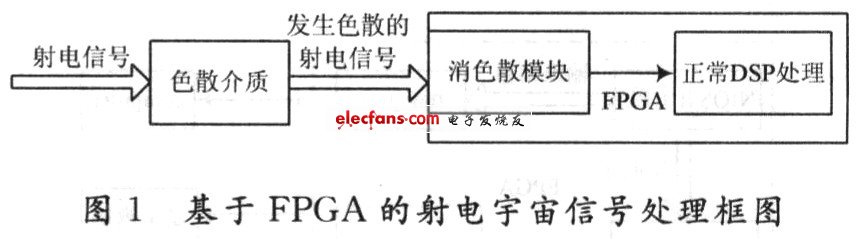

图1为基于FPGA的射电宇宙信号处理框图。

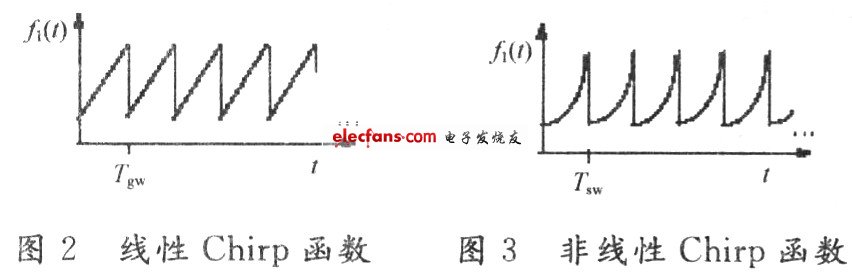

该设计是基于SoPC技术设计的Chirp函数信号发生器,该系统把微处理器模块和DDS模块集成到单片FPGA芯片内部,通过在嵌入式 *** 作系统μC/OS-Ⅱ编写的程序,实时控制微处理器对DDS的控制字输出,DDS模块根据频率控制字的不同,输出不同的数字化正弦波。使之符合Chirp函数的时变频率特征。Chirp函数根据输出频率的递变规律一般分为两种:线性Chirp函数和非线性Chirp函数,以下是两种Chirp函数在频域上的表现图如图2,图3所示。

从图2,图3可以看出Chirp函数的频率输出与时间的f-t关系可以总结为:

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)