电磁兼容性(EMC,即ElectromagneTIc CompaTIbility)是指设备或系统在其电磁环境中符合要求运行并不对其环境中的任何设备产生无法忍受的电磁骚扰的能力。因此,EMC包括两个方面的要求:

一方面是指设备在正常运行过程中对所在环境产生的电磁骚扰(ElectromagneTIc Disturbance)不能超过一定的限值;

另一方面是指设备对所在环境中存在的电磁骚扰具有一定程度的抗扰度,即电磁敏感性(ElectromagneTIc Susceptibility,即EMS)。

1 EMC设计与EMC测试的联系

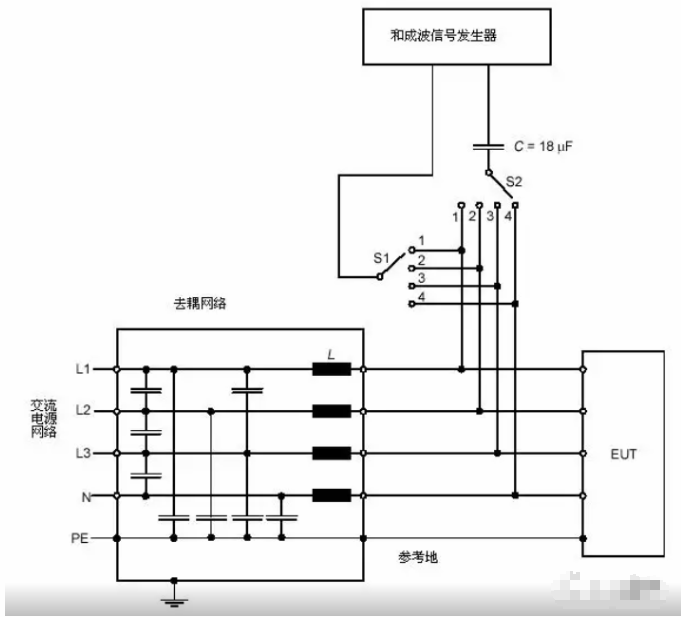

辐射度抗干扰度测试实质:共模干扰的测试

电源线浪涌测试有线-线(差模)和线-地(共模)两种注入方式,由于差模电流总是按照预期的路径返回源头,其定位于防护相对比较容易,而共模电流却由于总是留经无法预期的路径从而使得定位和处理也相对困难,因此,电源线浪涌测试实质就是共模干扰。

从产品的EMC测试原理分析,主要影响产品EMC测试结果的为共模干扰,因此,产品的EMC问题主要与共模干扰有关,对于产品EMC设计来说,重点关注的也是共模问题。

2 EMC设计方法和思路

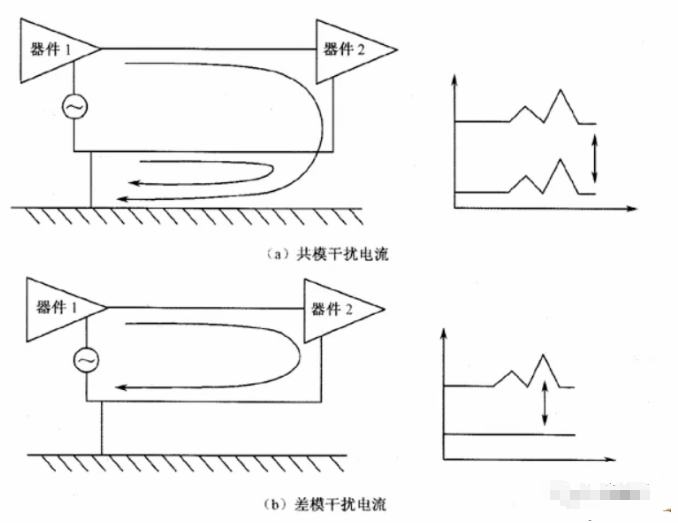

差模电流传送有用信号,其在信号路径和返回路径中均存在,两条线上的电流大小相等,方向相反

共模电流不包含有用信息,共模电流存在于信号路径、返回路径与地之间,两条导线上的电流大小相等,方向相同。

从水流与电流的共性与联系,我们可以受到启发,即共模电流在于“疏”,这就是产品EMC设计的核心思想。

电流始终沿着一条或几条闭合环路流动,使用共模电流和疏导的设计方法和思路,有利于我们控制电流按照为系统正确运行所希望的环路流动。

即在EMC设计时, 我们就需要屏通过蔽滤波、接地等设计手段或方法引导共模电流流向,控制共模电流流动的路径,避免共模电流流经不可预期的路径。

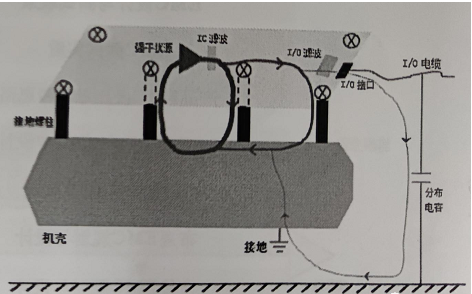

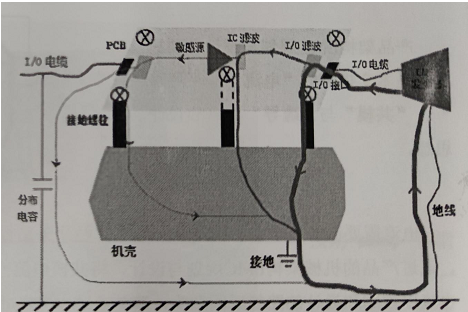

疏导共模电流降低EMI风险

从图可以看出,产品单板强干扰源产生的共模电流,首先经过IC滤波后和I/0滤波电路后,只有剩余很小的一部分共模 电流将沿着I/0电缆逃逸出机箱,因此,对外的风险也将大大减小。

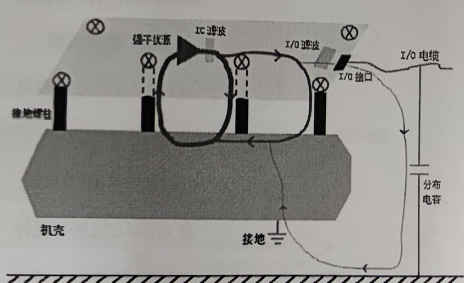

疏导共模电流提高EMS能力

从图可以看出,抗扰度试验注入的电磁干扰,经过I/0接口的防雷、滤波电路及IC等器件的外围,最终真正流过单板或流入敏感电路的干扰能量基本可以忽略,因此,旁路即疏导共模电流也就有效的保护了单板上的敏感电路,从而提高了产品的抗干扰性能。

3 PCB架构和EMC规划与设计

产品架构EMC规划与设计首要思路就是本文提炼的“电流”与“环路、“共模”与“疏导”的核心设计

电流需要流经一个完整的环路,回流流经哪条路径,取决于各条路径的共模阻抗。通过产品的机械架构EMC规划与设计,将共模电流“疏导”和“旁路”,引导共模电流以规划和设计的路径返回源头,避免或减少流经非预期的路径而导致EMC问题。

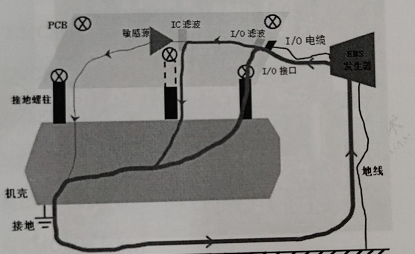

1.系统接地点靠近I/O接口干扰共模电流流向

当系统接地点靠近I/O接口时,一部分将 通过I/O线缆对地的分布电容到达参考接地平板,然后经过系统的地线返回源头,但是此时由于系统接地点靠近I/O接口,此时与系统接地点远离I/0接口时相比,形成的共模环路将大大减小,因此,对外产生的电磁干扰也将随之减小。

2.系统接地点远高I/O接口抗扰共模电流流向

当统接地点远离1/O接口时外部料合或注入的共模干扰电流,一部分将流经整块单板后并从信号接口另一侧靠近系统接地点的位置流入参考接地平板后返回源头,此时共模电流将流经整块单板及其敏感电路区域,因此,将造成产品抗扰度降低。

4 层叠EMC规划设计

回返电流:

电流是产生电磁干扰的根本原因,根据基尔霍夫电压定律和安培定律,电流永远需要一个完整的环路, 所有电流都要经完整的环路以回到其源头。

信号的传输路径是由两条相反的路径构成,一条 是驱动路径,由驱动端指向接收端,一条是返回路径,由接收端指向发送端,即任何电路既有信号路径又有回流路径。

磁通对消原理:根据麦克斯韦方程,磁通总是在传输线中传播的,如果射频回流路径平行靠近其相应的信号路径,则回流路径上的磁通(顺时针场)与信号路径上的磁通(逆时针场)是方向相反的,那么顺时针场和逆时针场相互叠加,则得到了通量对消的效果。

为消除PCB中的射频能量,在PCB设计中必须采用通量对消或通量最小化技术。PCB层叠EMC规划与设计的思路就是合理规划信号回流路径,使得磁通对消。

参考平面:

参考平面为射频电流提供一个返回源头的低阻抗的路径(通量对消或通量最小化)。

电源平面、地平面均能用作参考平面,电源平面作为参考平面时有较高的阻抗,而地平面作为基准参考电平,阻抗相对较低,其回流效果远远优于电源平面,因而,在选择参考平面时,应优选地平面。

采用电源层和地层作为参考平面时:

(1)电源平面的阻抗比地平面阻抗高:

(2)为降低电源平面阻抗,尽量将PCB的主电源平面与其对应的地平面相邻布置并且尽量靠近,以增大耦合电容,降低电源平面的阻抗;

(3)电源平面与地平面构成的板间电容与板上其它去耦电容结合,既可降低电源层的阻抗,又能有效的增加去耦带宽。

信号回流路径

当使用电源平面,地平面做为参考平面时,微带线因为信号布线与参考平面之间紧密耦合的缘故,回返电流会在参考平面上布线的直接正下方(或正上)流动。

对称带状线回返电流平均使用上下两个平面。非对称带状线常见于多层板,大部分的回返电流流经靠其最近的参考平面。

此处以常用四层板为例

由于信号层与回流参考平面相邻,S1紧邻地平面,有最佳的通量抵消效果,S2紧邻电源平面,因为电源平面由于许多器件开关状态的非对称性而产生通量相移,因此S2的通量抵消效果较S1效果要差。

电源平面和GND平面相邻,平面间距离很小,有最佳的磁通抵消效果和低的电源平面阻抗。

20H原则:当使用高速系统或高速时钟时,要求所有的电源平面要比与其相邻的地平面缩进20H (H

为电源层到地层的距离),即20H原则。

布线换层三种情况:

(1)布线参考平面不变

※此种情况下回返电流将在同一参考平面层流动,不需要加任何处理措施。

(2)布线参考平面从一个地层换到另一个地层

此种情况下回返电流在两个地平面上流动,则必须在布线换层的过孔附近设置一个地过孔连接两个地层。

(3)布线参考平面从地层(电源层)换到电源层(地层)

此种情况下回返电流分别在电源平面和地平面流动,则必须在布线换层的过孔附近设置去耦合电容将地层(电源层)与电源层(地层)连接起来。

5 布局EMC规划与设计

PCB是电磁干扰的来源,源头就是PCB的关键电路。PCB布局设计,就是重点考虑对各个模块电路以及关键电路如强干扰源、敏感源、滤波电路等等布局,将共模电流从空间上进行必要的隔离,控制在设计的范围之内,这就是PCB布局的核心思想。

首先进行模块划分:

A.依据功能进行划分, 如时钟电路、放大电路、驱动电路、A/D与D/A转换电路、I/O电路、开关电源、滤波电路等

B.依据工作频率进行划分, 如高频、中频和低频电路;

当需要在电路板上布置快速、中速和低速逻辑电路时,高速的器件(快逻辑、时钟振荡器等)应安放在紧靠边缘连接器范围内,而低速逻辑和存储器,应安放在远离连接器范围内。

C.依据信号类型进行划分, 如数字电路和模拟电路

对于数模转换A/D和D/A电路,应该布放在数字电路和模拟电路的交界处,器件布放的方向应以信号的流向为前提使信号引线最短,并使得模拟部分的管脚位于模拟地上方,数字部分的管脚位于数字地上方。

其次是PCB关键电路/器件的摆放位置

强干扰器件

时钟电路(包括晶体、晶振、时钟驱动)、开关电源、高速总线(如低位地址总线A0、A1、A2)、感性器件如继电器等,此类器件和电路有很强的干扰,布局时布置在单板中央,另外周边也需要布置滤波电路防止干扰扩散。

敏感器件

复位芯片、看门狗电路、低压放大器、模拟芯片、锁相环、小弱信号、IRQXINHAO 等,此类器件很容易受外界干扰,布局时布置在单板中央,另外周边也需要布置滤波电路防止干扰影响敏感器件。

I/O滤波器件

典型如光耦、隔离变压器等信号隔离器件以及RC、LC、 ∩等接口滤波器件,通常布置在I/O接口,布局时需要防止滤波失效,包括滤波器件布局及滤波器件周边强干扰或敏感器件导致滤波失效。

滤波电路布局:

去耦电容要尽量年近IC的电源管

电源滤波要尽量靠近电源输入或电源输出端口或器件电源管脚;

局部功能模块的滤波要靠近模块的入口;

对外接口的滤波(如磁珠)要尽量靠近连接器等。

6 布线EMC规划与设计

布线层的选择:

公优先考虑在内层布线

优先考虑无相邻布线层,或虽有相邻布线层,但相邻布线层垂直走线或对应布线区域下无走线

内层布线优先级别, LG-G>LG-P>LP-P,其中,LG-G 、LP-P分别表示两个地层、电源层之间的信号层,LG-P表示地层和电源层之间的信号层

关键信号线的布线层应有相邻的参考地层,并确保关键走线未跨分割区

参考平面展分割形式:

电源与地平面分割

当PCB上存在多种不同的电源或地的时候,通常不可能为每一 种电源或地网络分配一个完整的平面, 常用的做法是在一个或多个平面上进行电源或地分割。同平面上的不同分割区之间就形成了开槽。

密集过孔形成分割

密集通孔包括焊盘和过孔。通孔穿过地层或电源层而与之没有电气连接时,需要在通孔周围留一些空间(即隔离环)以便进行电气隔离:当通孔之间的距离太近时,隔离环就会重叠并相互连成-体,形成分割。

跨分割布线会造成如下的问题:

(1)回流路径中断或增大电流环路面积,增大了环路电感,影响信号质量;

(2)增加向空间的辐射干扰,同时易受空间电磁场的影响;

(3)增加与板上其它电路发生电磁场耦合的可能性;

(4)环路电感上的高频压降形成共模干扰源,并通过I/0电缆产生共模干扰。

如何减少平面层分割?

(1)对于IC核电源或单板用到较少的电源,避免在电源平面分割,可采用信号层布线或信号层覆铜减少电源平面分割;

(2)数字地与模拟地分割时需要进行评估,不要进行无意义的分割;

(3)数据总线、地址总线、控制总线换层时,避免过孔挨得太近且形成直线,以免在平面层形成分割;

(4)单板不要密集打接地过孔,避免在电源平面层形成分割;

(5)高密度接插件在引脚布置时均匀的安排地网络,保证电源/地平面的连续性,避免形成分割。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)