【导读】本SiC FET用户指南介绍了使用含快速开关SiC器件的RC缓冲电路的实用解决方案和指南。该解决方案经过实验性双脉冲测试(DPT)结果验证。缓冲电路损耗得到精确测量,可协助用户计算缓冲电路电阻的额定功率。本指南还在UnitedSiC_AN0018《开关含缓冲电路的快速SiC FET应用说明》中分析了缓冲电路对硬开关和软开关应用的有益影响。

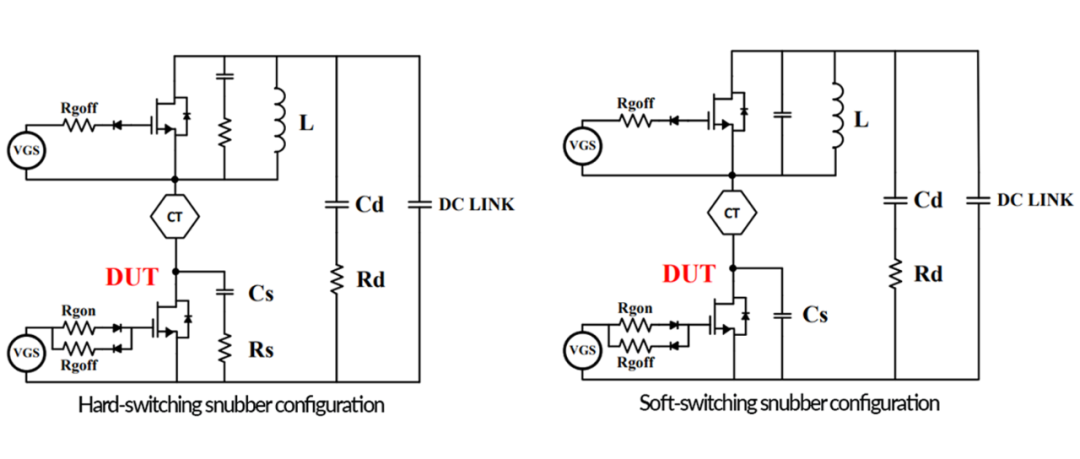

【图1.DPT示意图,硬开关(a)和软开关(b)中都有RC缓冲电路】

双脉冲测试器(DPT)采用半桥结构,有电感负载。图1“DPT示意图,硬开关(a)和软开关(b)中都有RC缓冲电路”是简化的示意图。当被测试器件(DUT)打开或关闭时,旁路电容器Cd提供瞬态能量,以便转换高侧(HS)和低侧(LS)器件的电流方向。这是瞬态功率回路。旁路电容器应设计在半桥布局附近,以降低瞬态功率回路中的寄生电感。在被测试器件的打开瞬态中,一旦完成换向,稳态的电流就从直流链路电容器流出,为负载电感器L充电,然后再经过被测试器件返回直流链路大容量电容器。这是稳态功率回路。当被测试器件关闭时,二极管变为前向偏压,且电感器电流流经二极管和电感器(续流回路)。为避免高dvdt诱发快速SiC器件打开,使用隔离的栅极驱动器和隔离的电源抑制高dvdt在栅极信号路径中诱发的共模噪音。这里提供了两个缓冲电路情形。有关详情,请访问https://unitedsic.com/appnotes/Snubber%20AppNotes_V8.pdf,参阅缓冲电路应用说明UnitedSiC_AN0018。

在设计总线缓冲电路时,Rd设计师应该注意Rd中的总能量耗散以免过热。

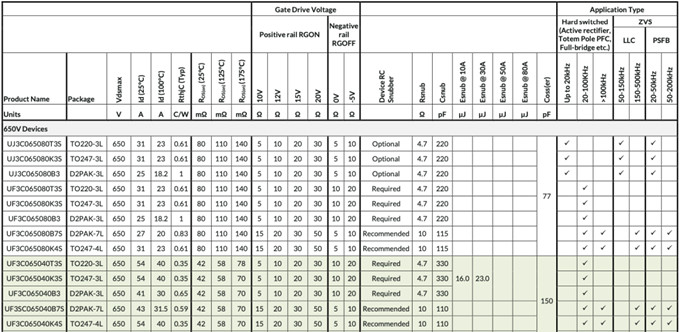

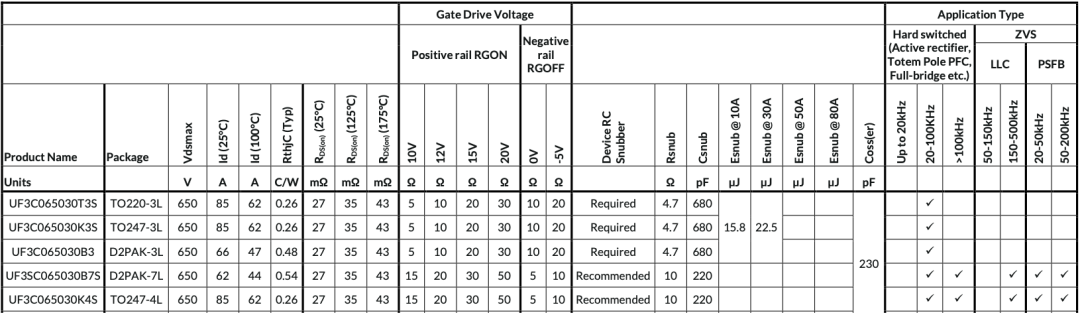

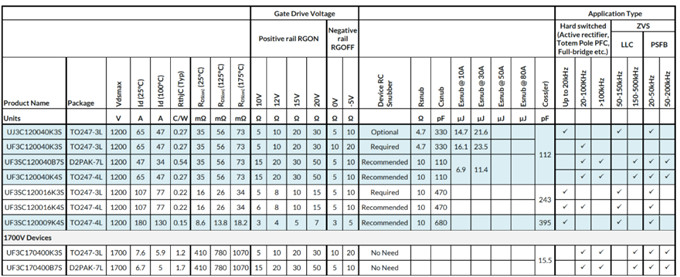

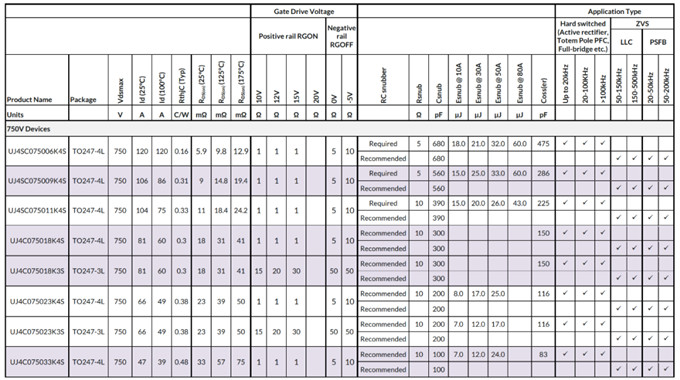

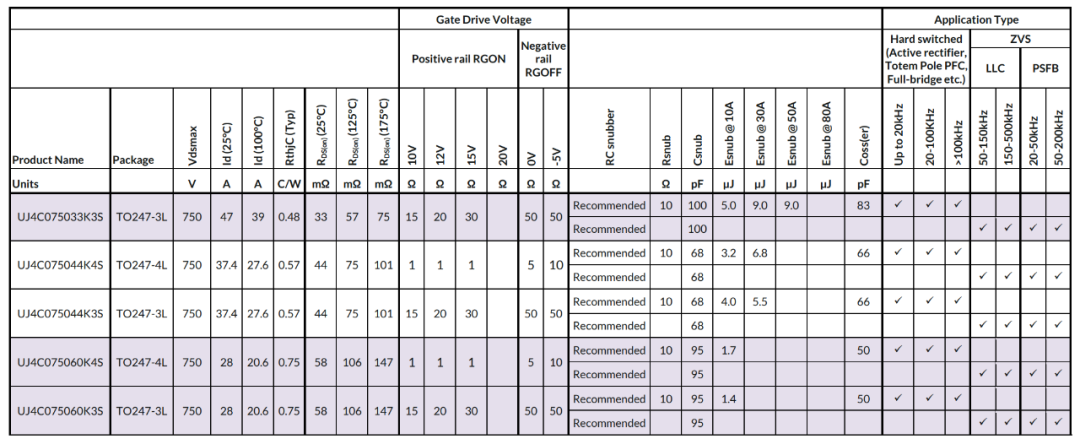

SiC FET Usage Table UJ3C and UF3C/SC Devices

在硬开关半桥应用中使用第三代产品的说明:

1. UF3CxxxyyyK4S效率最高。建议使用缓冲电路改善电磁干扰。

2. 搭配缓冲电路的UF3CxxxyyyK3S是3L应用的快速解决方案。用于硬开关时,采用3端子封装的UF系列必须使用缓冲电路。

在软开关半桥应用(LLC、PSFB等)中使用第三代产品的说明:

3. D2PAK-7L、TO247-4L效率最高,即使搭配缓冲电路电容器(无Rs)也是如此。

4.UJ3CxxxyyyK3S不需要缓冲电路。在RDS(on)>80m时,UJ3CxxxyyyK3S能非常好地平衡电磁干扰与效率。

5.含Cds电容器的总线缓冲电路通常具有出色的表现与波形。

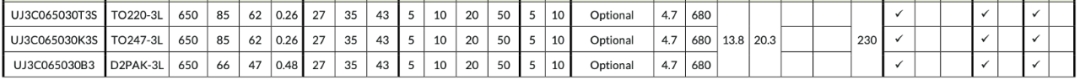

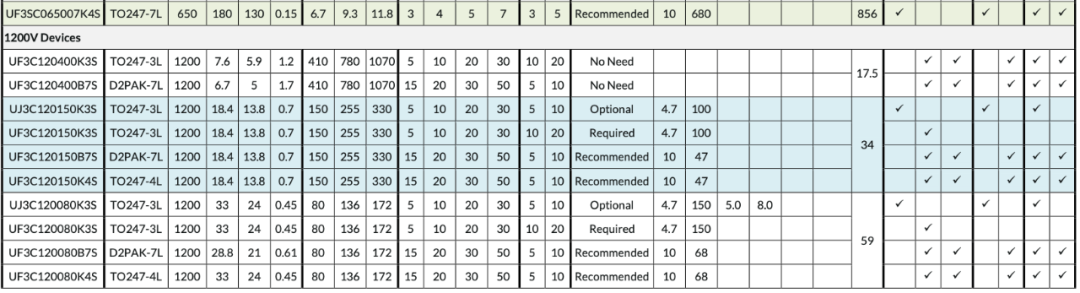

SiC FET Usage Table UJ4C/SC Devices

在硬开关半桥应用中使用第四代产品的说明:

1. 所有UJ4C器件都是在搭配2.5Ω,100nF的总线缓冲电路时测量的。

2. 所有UJ4CxxxK3S器件都需要搭配2.5Ω,100nF的总线缓冲电路或推荐的器件缓冲电路。

3. 如果开关电流超过20A,则需要器件缓冲电路。也可以选择搭配纯电容缓冲电路的总线缓冲电路,但是会导致过冲较高。

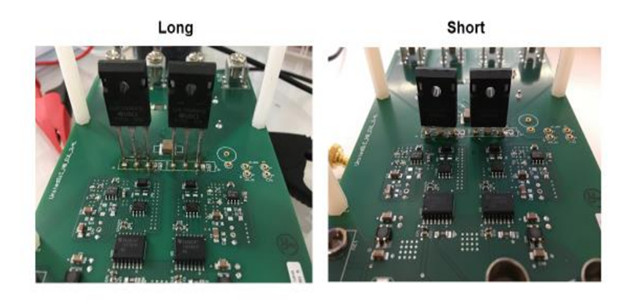

【图2:长引脚与短引脚的对比,通孔器件的引脚必须完全插入,以尽量减小电感】

缓冲电路设计指南

本SiC FET用户指南介绍了使用含快速开关SiC器件的RC缓冲电路的实用解决方案和指南。该解决方案经过实验性的双脉冲测试(DPT)结果验证。缓冲电路损耗得到精确测量,可协助用户计算缓冲电路电阻的额定功率。本指南还分析了缓冲电路对硬开关和软开关应用的有益影响。名为“开关含缓冲电路的快速SiC FET”的应用说明对本用户指南的内容进行了补充,要阅读该说明,请访问https://unitedsic.com/wp-content/uploads/2019/11/Snubber-AppNotes_V8.pdf。

有关更多缓冲电路指南,请访问https://info.unitedsic.com/fet-design-tips

基本假设:

1. Rgon:尽量减小Qrr,以降低Eon。

2. Rgoff:值很小,因而VGS波形更好。UFK3S需要Rgoff较高,以避免振荡。可以为零。

3. 共源共栅Rg对打开didt有巨大影响,而对dvdt的影响有限。

4. dvdt会被缓冲电路影响。

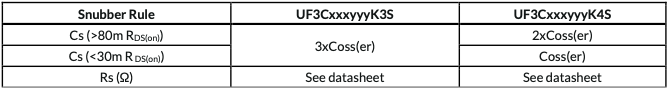

指南:

【说明:在软开关(ZVS)应用中使用缓冲电路Cs可以大幅降低Eoff。】

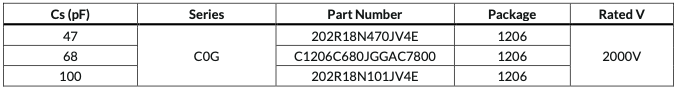

物料清单:

说明:

1. “C0G”陶瓷电容器在温度和电压变化时电容最稳定。

2. KEMET的X8G HV ClassI绝缘体的最高工作温度可达150°C,采用最新的高温绝缘技术,在温度极高的应用中和外壳应用中十分可靠。X8G的电容不随电压而变化,在环境温度变化时变化极小。对于电容较高、占地较大且电容不稳定的器件而言,它是适合的替代选择。在-55°C至+150°C下,它的电容变化仅为±30ppm/°C。KEMETX8R采用挠性端接技术,可阻止板应力传导到刚性陶瓷体,从而降低了挠裂风险,挠裂可能会导致IR低或短路故障。

说明:

1. “KTR18”电阻的额定电压为500V,过载电压为1000V。

2. “SR1206”电阻的额定电压为200V,过载电压为400V,绝缘耐受电压为500V。

3. TE连接采用3540系列的SMD电阻,在2817大小的封装中,70°C下,它可以处理4W功耗。

免责声明:本文为转载文章,转载此文目的在于传递更多信息,版权归原作者所有。本文所用视频、图片、文字如涉及作品版权问题,请联系小编进行处理。

推荐阅读:

雷达传感器如何显著提高智能家居的能源效率

如何提高系统功率密度

NFC接口保护如何选择合适的器件?

Xilinx FPGA DDR3设计(一)DDR3基础扫盲

基于事件的视觉传感器发展现状与趋势

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)