电子设计自动化(Electronic Design AutomaTIon,EDA)技术是新兴的电子设计自动化工具,是目前世界电子设计的最新技术方向和潮流 [1]。在数字电路实验中,EDA 作为一种重要的实验工具使传统数字电路实验的教学模式得到了改变,实验的 *** 作过程得到了一定的简化。

1 EDA 技术基本特征

EDA 作为现代电子设计的核心, 以大规模可编程逻辑器件(FPGA/COLD)为载体,以计算机为工作平台,在 EDA 软件开发环境下,采用硬件描述语言 HDL(Hardware DescripTIon Language)编写设计文件,而一系列的编译、综合及优化、布局布线、仿真 [1],直到编程下载等工作都可自动的完成。电路的逻辑功能与器件无关,采用的是用硬件描述语言实现,在整个硬件设计的过程中就像软件设计一样方便高效,对设计者的硬件电路方面的知识需求较低,各可编程器件之间可移植性好,因此适合多个设计者协同分工设计,可缩短开发周期。EDA 技术具备采用高级硬件语言描述的特点,能够实现系统级仿真具有较强的综合性能 [1]。它主要采用的是“自顶向下”和并行工程的设计方法, 使设计者一开始就将产品生成周期、成本、质量、开发时间等一系列因素考虑到其中。然后系在对系统进行设计的时候,需要先从整体要求入手,“自顶向下”将整个系统设计划分为不同的功能。在设计中每个阶段都可进行仿真,并及时改正设计中发现的错误。高层次系统采用硬件描述语言,最后具体的门级逻辑电路网表文件需要用逻辑综合优化工具来产生,而专用集成电路或印刷电路板的实现是对应的物理级得到的。

我校 EDA 实验室主要采用的是 Quar tusI I 软件。QuartusII 是 Altera 公司推出的一款综合性可编程逻辑器件开发软件,设计者可直接用硬件描述语言或原理图进行设计,对于内部器件不需要精通,且设计速度快。该软件最主要的特点为 :运行速度快、易学易用。

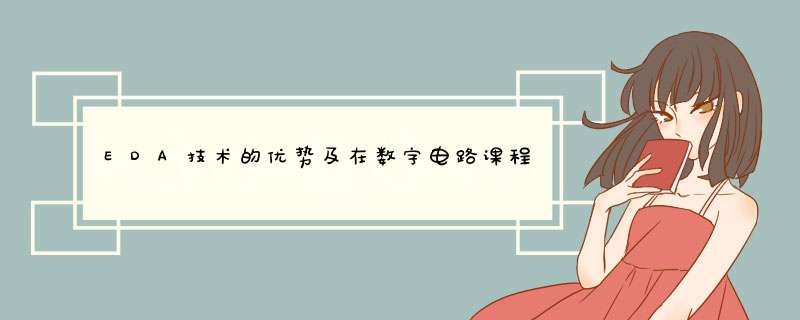

2 EDA 技术设计流程

EDA 技术设计流程如图1 所示。

(1)设计输入。一个设计项目可由单个或多个原文件组织而成,它们可以是原理图文件、混合输入文件、VHDL 文本文件等。

(2)综合。综合的关键是将 Verilog HDL 的软件转化为硬件电路,使两者进行挂钩,完成综合必须借助EDA 软件的综合器。对供应商提供的某一FPGA/CPLD 产品可针对其源文件进行综合。设计人员设计的逻辑电路图可利用 EDA 软件提供的逻辑综合和优化功能将其自动地转化为门级电路,同时还会生成对应的时序分析文件和网表文件。

(3)布线布局。在综合之后的网表文件利用布局/ 布线适配器针对某一具体的器件进行逻辑映射 *** 作,将其映射 *** 作(包括底层器件配置、逻辑分割、逻辑优化、布线等 *** 作)配置于目标器件中。

(4)仿真。在 EDA 设计中最重要的步骤就是仿真,即是下载编程前,利用 EDA 工具对适配产生的结果进行模拟测试。在EDA 设计过程中仿真可分为两种不同级别的仿真测试,即时序仿真和功能仿真。其中,时序仿真是完全考虑了器件的硬件特性, 并根据适配器产生的网表文件进行仿真,仿真精度较高,因为它最接近于器件的真实运行。功能仿真不会考虑到硬件特性,对设计者所描述的逻辑功能进行仿真,且完全满足设计者的要求。

(5)编程下载。通过仿真验证设计完成后,采用 Byteblaster 下载电缆线以 JTAG 方式将适配生成的下载或配置文件下载至FPGA/CPLD 器件内,方便于硬件的调试和验证。

上述步骤完成后,将统一对整个硬件系统进行测试,以便发现设计中的问题,得到及时的解决。

图1 EDA技术设计流程图

3 EDA 技术的优势及在数字电路课程设计中的应用

由于初学阶段对硬件电路的功能及特性的不熟悉,导致在连接电路时易出错,在检查错误过程中也会浪费大量的时间 和精力,一旦出错,将导致电路出现一些不正常或无法预知的实 验结果,最终使实验失败,甚至还可能会出现损坏电路元器件、实验测试仪器及一些无法预测的安全事故。引入 EDA 后的数字 电路实验可通过用硬件描述语言去描述电路的功能,将硬件采用 “软件”的方式去描述,大大降低了设计时间及设计难度。“自顶向下”的设计理念始终贯穿于 EDA 设计中,而人们也习惯于这种思维方式,因此电路设计的逻辑性较强,同时也便于学习思维的发展和提高。

传统的数字电路采用的是 TTL 逻辑器件进行设计连线,由于实验条件受限,且随着实验教学年限的增加,实验室设备的损坏、老化,需要定期的更新与维护,才能保证正常实验的进行。而电子技术的发展和更新日新月异,实验室的设备需要紧跟时代的步伐进行更新换代,多数学校设备的更新都不能紧跟技术的发展,将直接影响到学生对最新知识的掌握,传统实验的不足可由EDA 仿真软件弥补,只需在计算机实验室安装 EDA 软件即可。当学生熟练的掌握了 EDA 技术之后,可缩短数字电路实验的时间,对于所描述出的电路更容易进行修改与调试,也能激发学生的兴趣,这种将理论与实践联系起来的方式对于理论知识的掌握有很大的帮助。由于 EDA 技术十分广博,在课堂学习之外还留给学生更多的想象空间,学生可通过自主创新,提高对数字电路的创新能力。

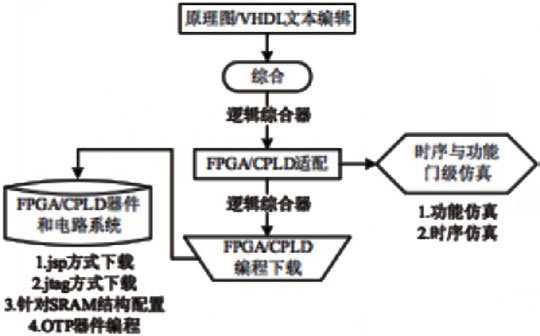

下面以设计一个五进制加法计数器为例来讨论 EDA 在数字逻辑电路实验中的具体应用。在此设计一个带有复位端的计数器, 端口分别为:clk(时钟,输入端,位宽为1),res(复位,输入端,位宽为1),cnt[2,0](计数端,输出端,位宽为3)。时钟 cl k 为上升沿触发,复位 r e s 低有效,计数端 cnt[2,0] 有效数据范围为3’b000~3’b100。程序流程图如图2 所示。

图2 五进制计数器流程图

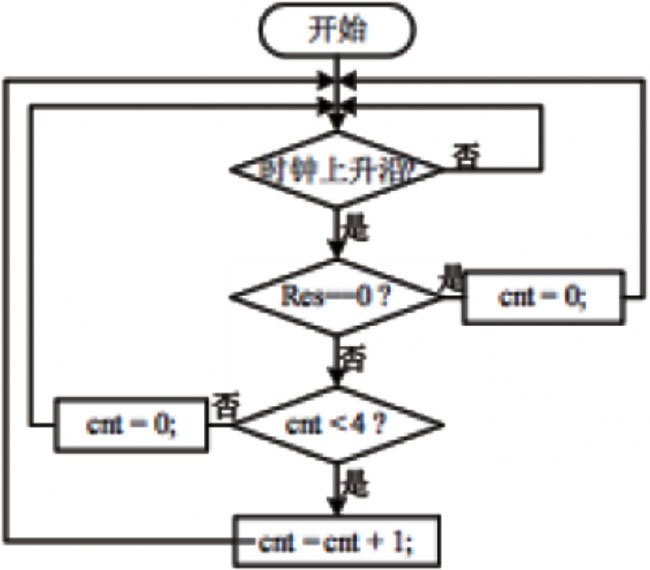

通过对五进制计数器的分析,用 VerilogHDL 描述出功能后, 在 Quartus II 11.0 软件上联合 Modelsim 进行仿真后,得到如图3 所示的仿真波形。

图3 五进制加法计数器仿真波形

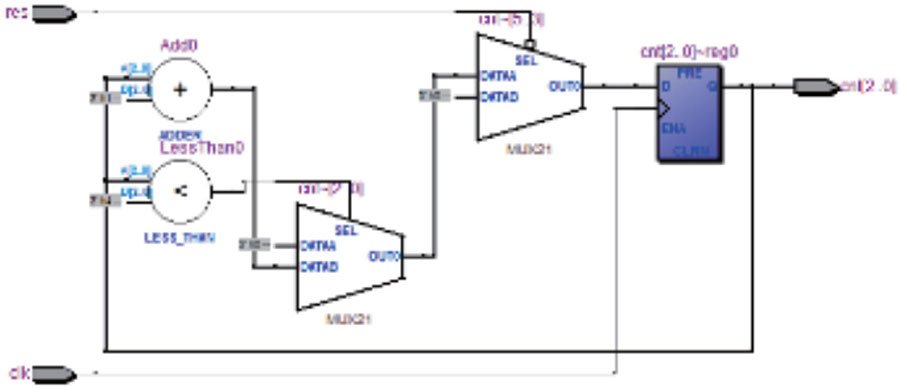

通过波形图我们可以看出,所设计的逻辑功能和设计要求完全一致,通过 QuartusII11.0 综合后的电路图如图4 所示,我们可以观察出五进制计数器有哪些基本的逻辑器件所组成,最后将设计的项目通过 Quartus II 11.0 软件下载 / 配置到相对应的实验箱, 学生可以很直观的观察到计数器的逻辑功能。

图4 五进制计数器综合电路图

我们必须熟悉各个逻辑器件以及要设计出的电路图的具体的组成,才能构造出总的电路图,而对于 EDA 技术我们只要了解了它的功能,根据它的功能用硬件语言描述出来,通过软件的综合后就可以得到对应的电路图。尤其是对于一些复杂的电路,利用 EDA 技术比传统的实验教学更简单方便, 更易掌握。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)