任务描述

设计一个2选1多路选择器。进一步熟悉Verilog HDL设计流程,组合电路的设计和测试。

相关知识

逻辑原理

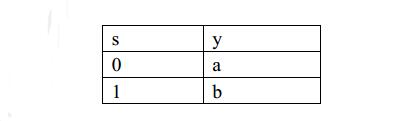

在数字信号的传输过程中,有时需要从多路输入数据中选出某一路数据,完成此功能的逻辑器件称为数据选择器,即所谓多路开关,简称MUX(MulTIplexer)。2选1多路选择器能在选择信号的控制下,从2路输入信号中选择其中的一路数据送到输出口。其真值表如下表所示。

多路选择真值表

编程要求

为了完成判断学生成绩等级的任务,编写的程序要能根据s输入的值给出相应y输出的值,满足多路选择器的真值表

源代码

测试平台:EduCodermodule mux21(a,b,s,y);

input a,b,s;

output y;

reg y;

always @(a,b,s)

// 请在下面添加代码,实现当选择信号S为0时选中a,为1时选中b;

/********** Begin *********/

begin

case(s)

1‘b0:begin y = a;end

1’b1:begin y = b;end

default:begin y = 0;end

endcase

end

/********** End *********/

endmodule

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)