由于DSP将超强的高速实时处理能力和丰富的外设功能集于一身,目前,以DSP为核心的嵌入式运动控制器已经成为开放式运动控制器的发展主流,并获得广泛的应用。本文通过 对运动控制器基本功能的研究,在分析、消化已有的基于DSP的运动控制器硬件资源基础上,开发了运动控制器的软件系统,详细介绍了运动控制器的软件设计。

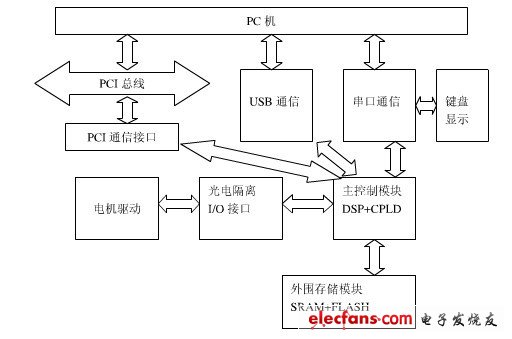

1 运动控制器硬件结构

图1 运动控制器硬件结构图

1.1 DSP+CPLD 主控模块

本系统采用了 TI 公司的 TMS320F2812 DSP 为控制核心,这是工业界首批 32 位的控制 专用、内含 FLASH 以及高达 150MHz 主频的数字信号处理器,专门为工业自动化、光学网络及自动化控制等应用而设计的。TMS320F2812 采用哈佛总线结构,有独立的程序和数据空间;具有很强的运算能力,能够实时地处理许多复杂的控制算法;片上内存丰富,可支持45 个外设级中断和 3 个外部中断,提取中断向量和保存现场只需 9 个时钟周期,响应迅速; 片上集成了多种先进的外设,包括两个事件管理器(EV)、12 位 A/D、两个串行通信接口(SCI)、一个串行外围接口(SPI)以及一个多通道缓冲串行接口(McBSP)等;其通用输 入/输出多路复用器(GPIO)拥有多达 56 个 I/O 口,在系统的软件开发中正是利用了这些丰富的内外设资源,才实现了系统要求的各种功能。

本系统中选用的 CPLD 是 Altera 公司 MAX3000A 系列的 EPM3128,这是一款高性能、 低功耗的基于 EEPROM 的 PLD。由于本系统的控制对象是步进电机,所以设计中主要利用TMS320F2812 的 GPIO 口进行电机控制接口与 I/O 接口的输入输出,但是由于 TMS320F2812是低功耗处理器,其 GPIO 引脚的输出驱动能力有限,而且由于 DSP 是主控核心,负载比 较多,所以将所有输出信号都经过 CPLD 驱动后输出,提高信号的驱动能力。此外,CPLD还用于系统电路的译码,增加系统设计的灵活性和可扩展性。

1.2 通信接口模块

本系统在用作插卡式运动控制时利用 PCI 总线实现 DSP 与 PC 的通信。PCI(PeripheralComponent Interconnect 外围部件互联)总线是 Intel 公司联合其他 100 多家公司于 1992 年推 出的基于新一代处理器的一种局部总线,是一种高性能 32/64 位数据/地址复用总线,能为 CPU 及外设提供高性能数据。PCI 总线具有严格的规范,目前已经发布了 PCI V1.0 和 V2.1规范,保证了其良好的兼容性;PCI 总线与 CPU 无关,与时钟频率也无关,可适用于各种平台,支持多处理器和并发工作;PCI 总线可以提供极高的数据传输速率,还具有良好的扩 展性。因此,PCI 总线在基于计算机总线的运动控制系统,即“PC+运动控制器”的结构中应用十分广泛。

本系统选用 CYPRESS 公司的 CY7C68001 芯片实现 PC 机和 DSP 之间的 USB 通信。CY7C68001 是通用 USB2.0 接口控制器,它是基于应用层编程的接口器件,相对于其它基于 链路层编程的接口器件,使用和开发都很方便。本系统采用 DSP 片上的 SCI 串行通信模块以及 MAX232 芯片转换成标准 RS-232 的通 信信号,实现正常的串口通信。

1.3 I/O 输入输出接口模块

本系统的输入/输出是通过 CPLD 的逻辑控制来实现的,以提高系统的工作可靠性和设 计柔性。考虑到运动控制器的可扩展性以及 DSP 的 GPIO 引脚的数量,共设计了 16 路数字量输出通道和 16 路数字量输入通道。数字量输出通道主要用于各轴方向、脉冲信号的输出以及一些外部设备的启停控制,如主轴及冷却液的开关控制等;数字量输入通道可根据用户 具体要求来定义其用途,如作为传感器接口,用于零点、限位信号的输入等。为提高系统应用的灵活性,系统输出采用了普通输出和差分输出两种方式,具体使用可由用户自行设定。

1.4 外围存储器模块

TMS320F2812 芯片内部包括 128KB 的 FLASH 和 18KB 的 SARAM,其中 128KB 的FLASH 用来存储系统软件程序已经足够,但是在实际使用中,考虑到运动控制指令和加工程序需要通过 USB 总线或 PCI 总线下载到运动控制器中,且 DSP 在工作过程中需要处理大 量的数据,仅依靠 DSP 芯片内部的存储空间远远不够,所以考虑外扩一片 FLASH 和一片SRAM 作为用户加工程序存储器和系统的工作存储器,它们通过 CPLD 完成与 DSP 之间的读写 *** 作。

本系统选用了 Intel 公司的 E28F128 FLASH 和 ISSI 公司的 IS61LV51216SRAM。E28F128 是一种采用 CMOS 工艺制成的 8MB FLASH,其读写访问时间为 150ns,此读写周期已经 大于 DSP 对外部端口的读写周期,为了能够和 DSP 的读写周期进行匹配,在对 FLASH 进 行读写 *** 作过程中必须插入等待周期。IS61LV51216 是一种高速异步静态 512KB 的 SRAM, 其读写周期为 10ns,与 DSP 之间可以无需插入等待周期便可以进行读写 *** 作,并可以直接映射到 DSP 外部存储接口的 Zone2 或者 Zone6 区域。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)