美国佐治亚理工学院(Georgia InsTItute of Technology)、韩国KAIST大学和Amkor Technology公司在“ISSCC 2012”上,共同发布了将277MHz驱动的64核处理器芯片以及容量为256KB的SRAM芯片三维层叠后构筑而成的处理器子系统“3D-MAPS:3D Massively Parallel Processor with Stacked Memory”(论文序号:10.6)。

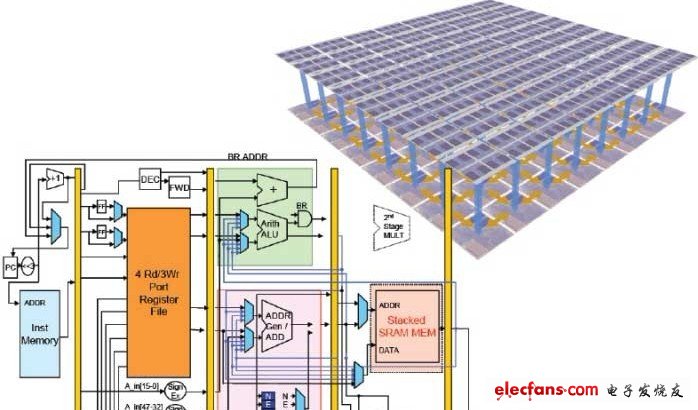

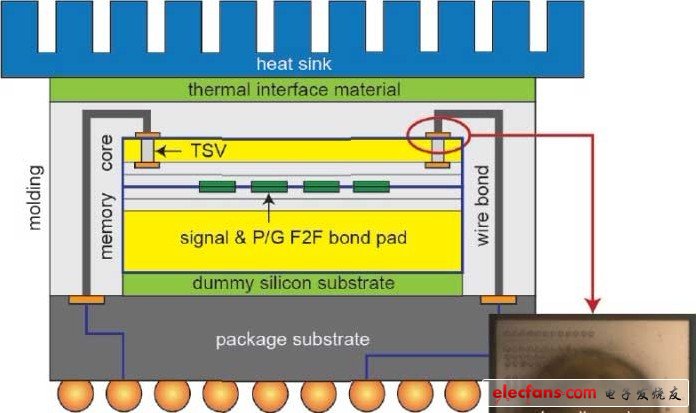

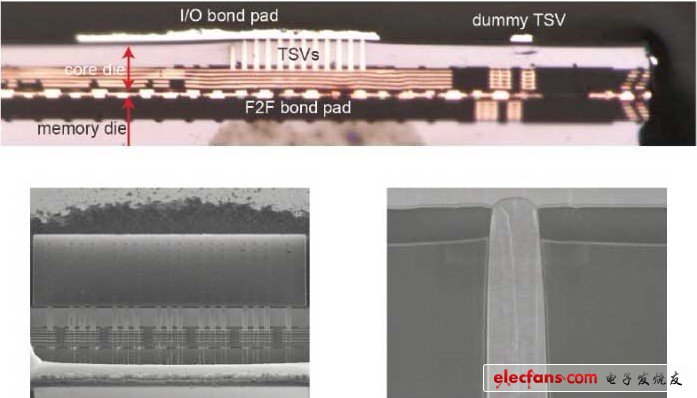

64个处理器内核分别与4KB的SRAM(数据存储器)三维连接,可通过最短的布线长度访问存储器。上下芯片将电路面相对,利用美国的三维IC技术开发公司Tezzaron Semiconductor拥有的芯片层叠技术,通过Face-to-Face(F2F)的铜键合工艺进行连接。在厚度为765μm的存储器芯片上,层叠厚度仅为12μm的处理器芯片。连接上下芯片间的信号线以及电源线和接地线全都采用F2F键合。F2F键合约有5万个,直径为3.4μm,间距为5μm。而且,还针对上层处理器芯片的输入输出,采用了将处理器芯片上下贯通的硅通孔(TSV,Through Silicon Via)。TSV约有5万个,直径为1.2μm,间距为5μm。

据介绍,使用试制的子系统并行运行AES加密、动作检测等共计8个应用时,实现了预期的内存带宽(Memory Bandwidth)。以4W的耗电量实现了最大64GB/秒的内存带宽。另外,在对数据存储器进行读写试验时证实,TSV以及F2F键合可以正常发挥作用。

此次试制的64核处理器芯片采用5段2路VLIW架构,利用美国GLOBALFOUNDRIES公司的130nm技术制造,芯片面积为25mm2。该处理器芯片配备约3300万个晶体管。在1.5V电源电压下工作,耗电量最大为6.3W。

在此次发布的双芯片层叠型系统(“3D-MAPS V1”)中,TSV的应用仅限于处理器芯片的输入输出。目前正在开发新一代系统——将2枚128核处理器芯片(内置SRAM)和3枚DRAM芯片(每枚芯片的存储器容量为64MB)共计5枚芯片三维层叠的子系统“3D-MAPS V2”。除了处理器芯片的输入输出外,3D-MAPS V2还计划在处理器访问DRAM时利用TSV。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)