SRAM 被广泛应用于计算机、手机、数码相机、汽车电子和医疗设备等电子产品中”,其快速存取和不需要周期刷新等特点对提高系统的可靠性、改普系统性能具有至关重要的作用。根据国际半导体技术蓝图(ITRS)报告,在MPU 产品和高性能ASIC占芯片面积的比例达到50%以上,且随着集成电路工艺技术的进步和集成度的提高,比例不断增大。现代数字集成电路中的SRAM 设计都采用CAD 工具,根据设计参数自动生成,设计者的自主性较小,对功耗、版图面积的优化较为困难,尤其针对一些特定应用时,半定制的设计方法存在明显的不足。本文采用全定制方法,设计了一款8x8 bit SRAM,主要应用于传感器、测量设备等数据存储量少、功耗和成本低的设备中。

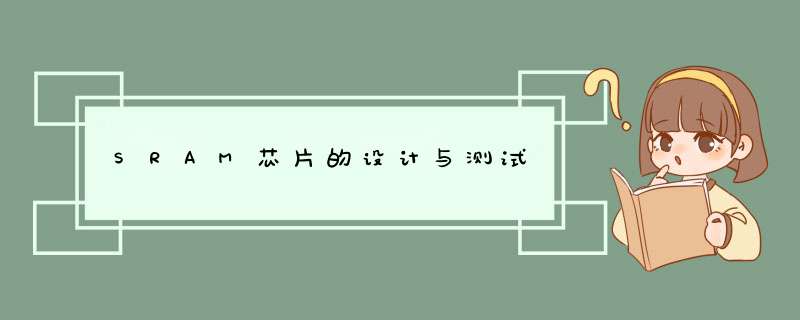

2SRAM 的整体结构SRAM 主要由存储阵列和外围电路构成,本文设计的SRAM 结构如错误! 未找到引用源。所示。其中,存储阵列是SRAM 的存储核心,外围电路主要包括地址译码器、灵敏放大电路、预充电路、多路选择器和控制电路。通常情况下,存储单元排列成方阵,行译码电路和列译码电路用于在读或写 *** 作之前定位存储单元。灵敏放大电路用于读出存储单元数据时将其电压放大,加速读 *** 作。控制电路中使用时钟信号和)↑选信号共同控制SRAM 的读写 *** 作。

存储单元

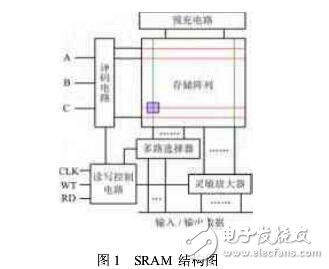

SRAM 的存储单元使用传统6 管单元,如图2所示。该单元由两个交叉耦合的反相器连接到两个NMOS 存取构成。由节点Q 和节点QB 共同存僻数据,其中节点QB 为节点Q 的反相。

图2 6管SRAM 单元电路图

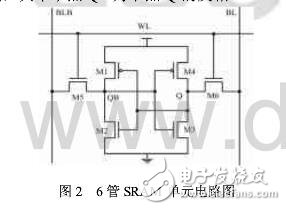

使用Hspice 仿真该单元的读写过程,可得存储单元的读延迟约为22.55 ps,写延迟约为49.03 PS。仿真得到该单元静态噪声容限(SNM)的蝶形图如图3 所示,SNM 约为1.03 V。

图3

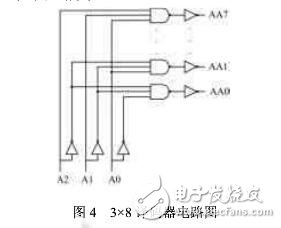

译码电路SRAM 存储器能够基于地址译码器随机存取数据。译码器可以在读写 *** 作开始之前确定存储单元,减少封装管脚数,从而减小外围电路的而积和功耗。通过译码电路,可以用M 个地址来表示2¥个存储单元,如图4 所示。

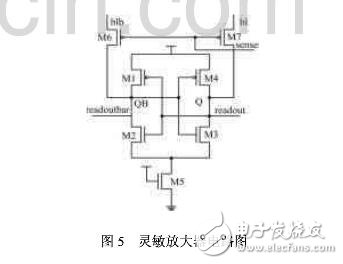

灵敏放大器(Sense Amplifier,SA)的作用是放大位于位线与输出缓冲单元之间,可以放大两信号,根位线上微小的电位差,输到下一级电路。本文采用锁存型灵敏放大器,它在速度、工艺敏感度和良品率等方面表现得比较优秀,如图5 庐信号控制两个PMOS 晶体管M6 和M7示。

S en s e的导通状态,实现数据的读出控制,同时也起到隰离保护位线的作用。对于晶体管M5,M6,M7,羔要增加其宽度来减小由此引起的延迟,提高灵敏放大器的速度。

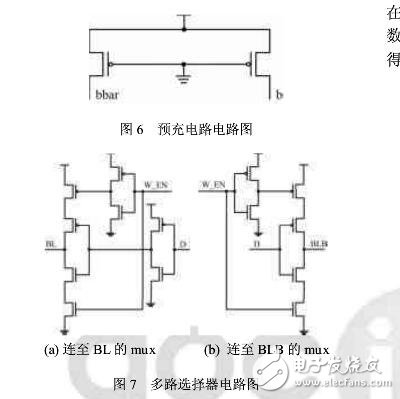

本设计使用较为简单的预充电路,如图6 所示。该电路由两个弱PMOS 管组成,棚极接地。除了读和写过程,该预充电路可以使位线BL 和BLB处于较弱的高电平状态。

多路选择器

多路选择器(mux)也称为数据选择器,连接在位线BL 和BLB 上,在写 *** 作过程中,两个多路选择器分别控制两根位线数据的写入。图7(a)为连接到BL 的多路选择器,图7(b)为连接到BLB 的多路选择器。只有写使能信号W _EN 为高电平时,数据D才能传输到位线上,由此来控制数据的写入。

SRAM 的电路仿真

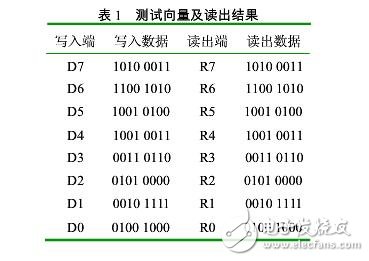

由于本设计主要应用于传感器、测量设备等数据存储量少、功耗和成本低的设备中,所以单端口SRAM 已经能够满足设计要求。将SRAM 单元排列成8X8 的阵列,连接到外围电路,通过时钟信号和片选信号共同控制读写使能信号,最终得到总体的SRAM 电路图。为了保证SRAM 电路功能和性能,采用测试向量进行仿真,测试向量及仿真结果如表1所示。

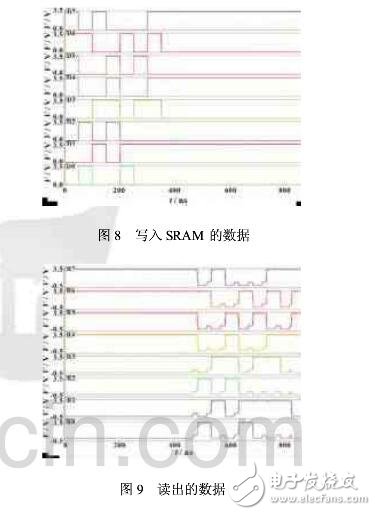

时钟频率为20 MHZ 时,遍历OOO 到111所有地址(即可遍历所有存储单元),输入测试向量。图8 所示为写入的数据D0~D7,该波形同表1所示的测试向量对应。数据写入后,读取写入的数据,读出的数据如图9 中的R0~R7 所示。对比发现,在时钟频率为20 MHZ 时,SRAM 能够较好地完成数据的写入和读出,逻辑功能无误。此外,可以得读延迟约为6ns。

SRAM 版图通过全定制设计方法实现,面积约为(0.299x0.275 )mm2。版图通过了DRC,ERC,LVS等物理验证和后仿真时序验证,最后导出GDSI 数据文件,交付工艺线流片生产。流片后显微照片如图10 所示。

为完成SRAM 芯片的测试,需要设计测试电路板。测试电路板主要提供测试接口和电源。芯片的控制信号和数据信号由红色飓风II-Xilinx FPGA 开发板提供,使用ISE13.2 软件建立测试工程,编写Verilog 测试程序(主要包括按照时序提供分频后的测试时钟、数据信号和控制信号),通过JTAG 下载到FPGA 的PROM 中,重新上电进行测试,通过RIGOL DS1102CA 双通道示波器捕捉信号,硬件测试平台如图11所示。

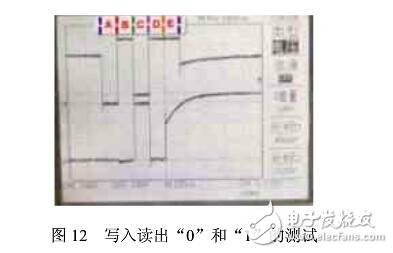

将示波器的通道1连接到写使能信号,通道2连接到数据端D7。如图12 所示,上方的波形为通道1接收的数据,下而的波形为通道2接收的数据。设计输入向量测试,当地址为OOO 时,将片选端CS置为低电平,图12 中,A区WT=*0”,RD=“1“,RD= “0”,读出写入数据 为“0”; B区WT=“1”,数据为“0”; C 区WT=“0”,RD=“1”,写入数据为“1”D 区WT-“1”,RD-“1”,为了更好地观察读出“1”时端口的电平变化,该段不进行读写,在输出端口上加弱的低电平信号; E 区WT=“1”,RD= “0”,读出数据为“1”,可明显地看到读出数据“1”的过程。从图中可以看到数据“0”和“1”被成功地写入和读出。

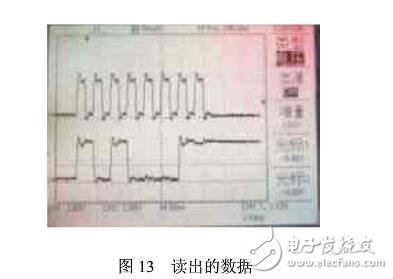

为验证实际的芯片是否可以达到设计指标,参考仿真方法,输入如表1中的测试向量,以D7为例,写入10100011后读出SRAM 中的数据,波形如图13 所示。遍历OOO到111所有地址,写入并读出数据,验证每个数据端是否能够正常工作,结果显示每个数据端口功能正确。

存取时间也是SRAM 的一个重要参数,它可以表示存储器的工作速度,图14 为测量读“1”时的存取时间。测量得到,存取时间=299.4 ns- 293.2测量存取时间时,不同的数据端口会有ns=6.2 ns。较小差别,这与实际芯片制造和不可避免的测量误差均有关。

测试可知: 当电源电压为3.3MHZ。工作时,测得电作正常,工作频率可达20源上的最大电流约为1.8545由此可得功耗丝mA,为6.11985mW。

总结本文基于Chartered 0.35EEPROM CMOSum工艺,采用全定制方法设计了一款8x8 bit SRAM 芯片。给出该SRAM 的整体结构,并分别介绍了各外围电路模块的设计。完成整体电路仿真和全定制版图设计,最后流片。芯片封装后,搭建测试平台进行测试。测试结果表明,在时钟频率为20 MHZ 条件下,芯片功能正常,性能达到设计要求,存 时间约6.2 ns,功耗约6.12mW。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)