1 引言

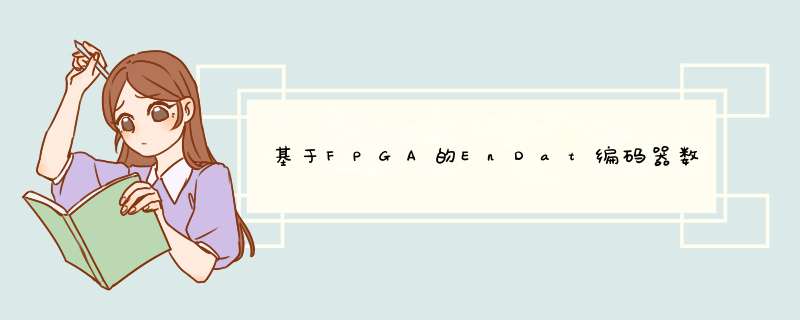

EnDat接口是HEIDENHAIN专为编码器设计的数字式、全双工同步串行的数据传输协议,具有传输速度快、功能强大、连线简单、抗干扰能力强等优点,是编码器、光栅尺数据传输的通用接口。由于使用了串行传输方式,所以只需四条信号线,在后续电子设备的时钟激励下,数据信息被同步传输。数据类型(位置值、参数、诊断信息等)由后续电子设备发送给编码器的模式指令选择决定。编码器利用自然二进制、循环二进制(格雷码)或PRC码对码盘上的物理刻线进行光电转换,将连接轴的转动角度量转换成相应的电脉冲序列并以数字量输出。它具有体积小、精度高、接口数字化及绝对定位等优点,被广泛应用于转台、机器人、数控机床和高精度伺服系统等诸多领域。

2 EnDat接口介绍

2.1 EnDat接口的特点

(1)高性能低成本:通用的接口适用于所有的增量和绝对式编码器,更经济的电能消耗,小的尺寸和紧凑的连接方式,快速系统配置,零点可根据偏置值浮动。

(2)更好的信号质量:编码器内部特别的优化提高了系统精度,为数控系统提供更好的轮廓精度。

(3)更好的实用性:自动系统配置功能;数字信号提高了系统的可靠性;监控与诊断信息有利于系统的安全;冗余码校验有利于可靠的信号传输。

(4)提高了系统的安全性:两个独立的位置信息及错误信息位,数据的校验和应答。

(5)适用于先进的技术发展:(高的分辨率、短的控制周期,最快16 M时钟,安全设计理念)适用于直接驱动技术。

2.2 EnDa2.2编码器性能的提高

(1)传输位置值与附加信息可同时传输:附加信息的类型可通过存储地址选择码选择。

(2)编码器数据存储区域包括编码器制造商参数、OEM厂商参数、运行参数、运行状态,便于系统实现参数配置。

(3)EnDa2.2编码器实现了全数字传输,增量信号的处理在编码器内部完成(内置14 Bit细分),提高了信号传输的质量和可靠性,可实现更高的分辨率。

(4)监控和诊断功能,报警条件包括:光源失效、信号幅值不足、位置计算错误、运行电压太低或太高、电流消耗太大等;当编码器的一些极限值被接近或超过时提供警告信号。

(5)更宽的电压范围(3.6~14 V)和传输速率(16 M)。

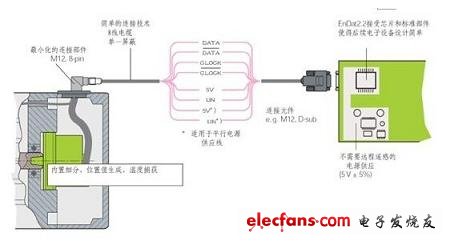

2.3 时序和OEM数据存储

在每一帧同步数据传输时一个数据包被发送,传输循环从时钟的第一个下降沿开始测量值被保存,计算位置值。在两个时钟脉冲(2T)后,后续电子设备发送模式指令“编码器传输位置值”(带或不带附加信息)。在计算出了绝对位置值后(见图2),从起始位开始编码器向后续电子设备传输数据,后续的错误位F1和F2(只存在于EnDa2.2指令中)是为所有的监控功能和故障监控服务的群组信号,他们的生成相互独立,用来表示可能导致不正确位置信息的编码器故障。导致故障的确切原因保存在“运行状态”存储区,可以被后续电子设备查询。

从最低位开始,绝对位置值被传输,数据的长度由使用的编码器类型决定。传输位置值所需的时钟脉冲数保存在编码器制造商的参数中。位置值数据的传输以循环冗余检测码结束。

位置值如果带附加信息,紧接在位置值后的是附加信息1和2,他们也各以一个CRC结束(见图3)。附加信息的内容由存储区的选择地址决定,然后在后面的采样周期里被传输。在后续的传输中一直传输该信息,直到新的存储区被选择。在数据字的结尾,时钟信号必须置高电平。10~30μs或1.25~3.75μs(EnDat可编程的恢复时间tm)后,数据线回到低电平,然后,新的数据传输可在新的时钟信号下开始。

同时,编码器为参数提供了不同的存储区,它们可以被后续电子设备读取,这些区域可以被编码器制造商、OEM厂商甚至最终用户写入。一些特定的区域是可以被写保护的。不同系列的编码器支持不同的OEM存储区和不同的地址范围。因此,每一个编码器必须读取OEM存储区的分配信息。基于此原因,后续电子电路应基于相对地址编程,而不能使用绝对地址。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)