TI C6000系列的DSP的内部总线架构、存储系统和各种外设(如EDMA3和PRU等),特别是片内的程序数据RAM和Cache系统,以及外设的EDMA控制器,Video port,McBSP,McASP以及SRIO接口等。

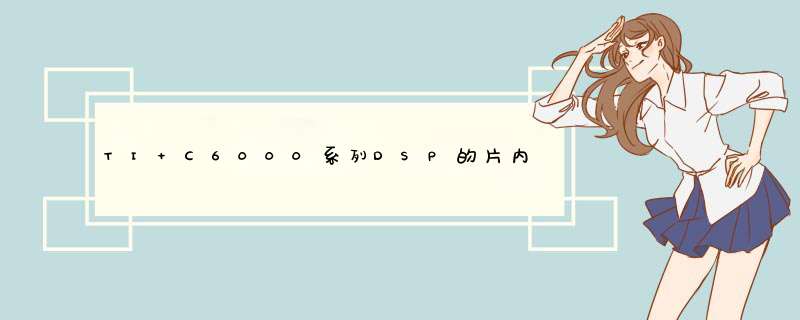

片内总线带宽

C62x: 两个32-bit的加载和存储总线;

C67x: 两个64-Bit加载,32-bit的存储总线;

C64x, C674x, C66x: 两条64-Bit加载和存储总线;

图1. C6000的片内总线宽度

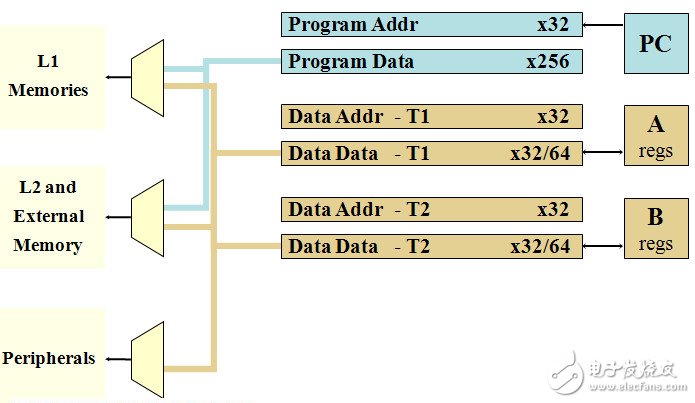

C6000系列DSP的片内系统框图

图2. C6000系列DSP的片内系统框图

一些设备包含速度更低点的L3 RAM

外部存储器:DDR2/3, SDRAM, 异步存储器

MegaModule/CorePac模块:

CPU

L1 RAMs/Cache

L2 RAMs/Cache

EDMA/EDMA2/EDMA3控制器等

Switched Central Resource (SCR)/TeraNet for C66x设备

Central crossbar switch,中央交叉通道转换器

从CPU和主外设设备如EMAC, USB, PCIe到从外设设备如SPI,I2C,McBSP等的通路

C66x的相对于C64x+的增强

只有一套统一的总线而不是SCR

所有的内存的处理都交给EDMA控制器完成;

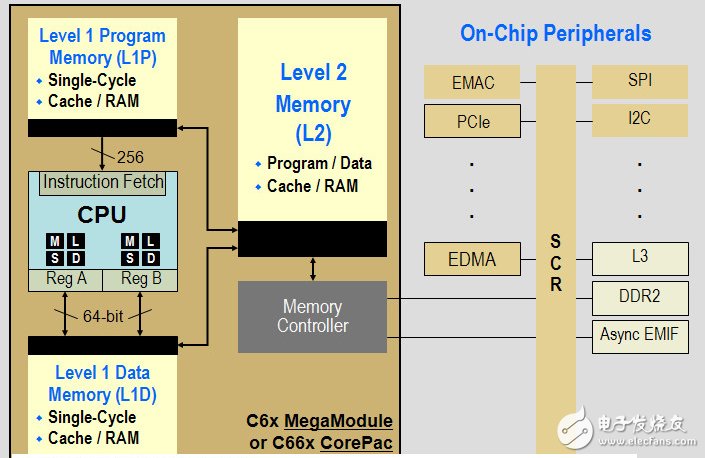

DM644x Davinci达芬奇处理器的内部总线框图

DM644x Davinci达芬奇处理器的内部总线框图

主设备发起数据传输

从设备只能按命令进行数据传输,但是从设备可以通过向CPU或者EDMA3发送传输请求中断来发起传输;

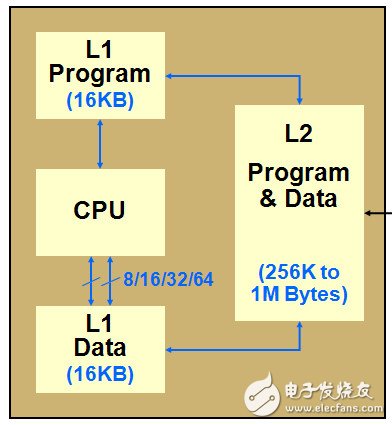

C64x的片内存储

图4. C64x的片内存储

L1P Cache控制器

直接映射(Direct Mapped (1 way))

和CPU同频率,大小为16KB,每个cache Line大小为8条指令,即32字节

L1D Cache控制器

2-way Cache

和CPU同频率,大小为16KB,每个cache Line大小64字节

L2 RAMs、Cache控制器

C6414/15/16 = 1M Byte

C6411/DM642 = 256K Byte

C64x+中加入了IDMA单元来进行以上3个内部存储器的数据传输,还可以从片内存储到config配置寄存器。

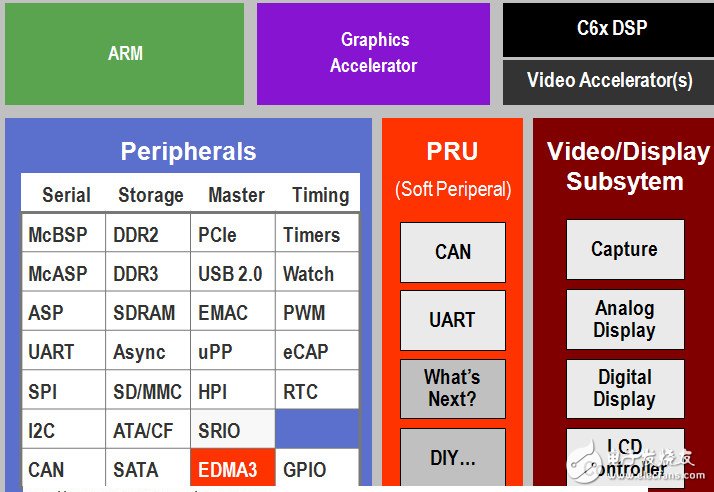

C6000系列DSP的外设

图5. C6000系列DSP的外设

EDMA3控制器

DMA来完成内存间或者内存到外设,外设到内存的数据传输,可以通过外部的设备事件来驱动同步,可以处理多达64个事件。DSP和ARM都能访问DMA通道资源,而对于从C64x+加入的IDMA而言,只有DSP才能访问其通道资源。

另外还有QDMA通道(Quick DMA),可以进行内存间的DMA传输,必须是异步处理,即必须由CPU来发起,一般的DSP上会有4-8个QDMA通道。

这些DMA通道间会共享一些资源,包括128-256个参数组( Parameter RAM sets (PARAMs)),以及64个传输完成标志位(TCCS)以及2-4个传输挂起队列。

主外设

VPSS (以及其他主设备)

USB, ATA, Ethernet, VLYNQ会共享SCR的访问;

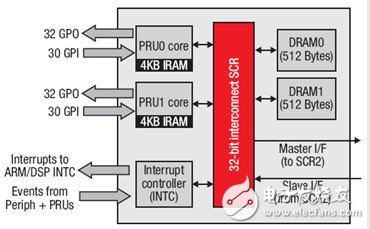

PRU(Programmable RealTIme Unit)控制器

图6. PRU框图

PRU包括2个独立的实时RISC核(大概只有40条指令,进行逻辑,算术和流程控制等),能软件编程来实现外设,访问GPIO针脚,PRU还有自己的中断控制器,还可以通过SCR来访问内存,同时还能完成功耗管理控制,如关闭ARM或者DSP,以及根据系统事件尽可能的关闭处理器或者唤起处理器。

管脚复用,即通过编程来定义管脚,实现你需要的外设。

多通道缓冲串口McBSP(MulTI-Channel Buffered Serial Port)

2/3个全功同步串口;

最高速率能到100Mbps

支持SPI总线协议

支持多个通道的处理 (T1, E1, MVIP, …)

多通道音频串口McASP (MulTI-Channel Audio Serial Port)

支持多达8个立体声 (16个通道)

I2C support

单独的SPI或者I2C设备;

SRIO(Serial Rapid IO)

高速的串行传输,如C6455设备支持4个SRIO接口,可以进行链式连接通信;每个接口的数据传输速度达到3.25Gbps(足够支持一路的1080P的HD视频了),可以跟SRIO switch,hub以及FPGA连接进行高速的数据传输。

时钟和计数器Timer / Counter

32-bit timer/counters可以用来产生中断;

64-bit的timer/counters可以用来对算法进行评估;

Ethernet EMAC

10/100 Ethernet MAC,PIN和PCI复用;

TCP/IP协议栈 stack由TI提供的NDK

一些更新的设备支持10/100/1000 Ethernet MAC

Video Ports (DM系列Davinci处理器)

用于视频图像的采集和显示;

两个8/10-bit BT656或者raw RGB模式;

16/20-bit raw模式或者高清应用的20-bit Y/C模式

支持8-bit的行缩放和色度重采样

本文主要介绍TI C6000系列的DSP的内部总线架构、存储系统和各种外设(如EDMA3和PRU等),特别是片内的程序和数据RAM和Cache系统,以及外设的EDMA控制器,Video port,McBSP,McASP以及SRIO接口等。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)