1 系统硬件设计

1.1 主要器件选型

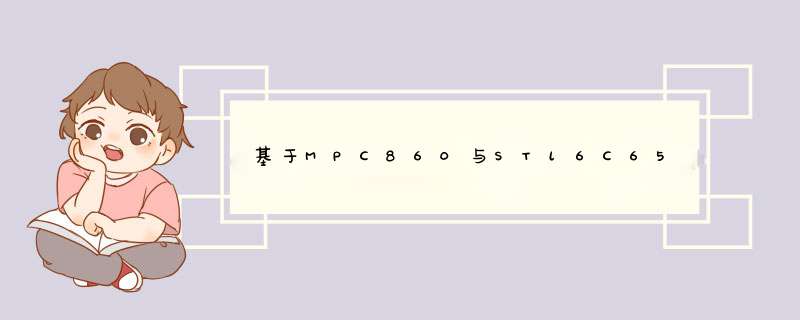

1.1.1 MPC860型微处理器

MPC860 PowerQIUCC(简称MPC860)内部集成了2个处理单元。一个处理单元是嵌入的PowerPC核(PowerPCCore),是主处理单元(CPU),是一个RISC芯片,通常编译后的程序指令都是由它执行;另一个处理单元是通信处理模块CPM(CommunicaTIons Processor Module),内部集成有一个RISC微处理器,对各种常用的通信模块进行管理。通信处理模块内部集成有4个串行通信控制器SCC、2个串行管理控制器SMC、1个串行外围接口电路SPI和1个I2C接口。另外,还有一个系统接口单元SIU,主要功能是提供内外总线的接口及一些其他功能(如SIU中断)的管理等。本设计利用通信处理模块CPM强大功能,与STl6C654通信。MPC860硬件结构如图1所示。

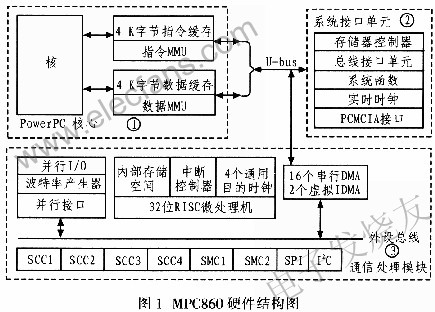

1.1.2 STl6C654

STl6C654是一个带有收发各64 Byte的FIF0的扩展通用异步收发器,自动软硬件流程控制,速率最高达到1.5 Mb/s(24 MHz时钟),支持16(Intel)/68(Motorola)总线接口类型。STl6C654结构图如图2所示。扩展的4路串口通道,每个通道有15个(64/68pin封装)或16个(100pin封装)内部寄存器,用来存放收发数据以及配置该串口的工作模式,需要在初始化时对各寄存器进行配置。工作模式有中断模式和定时查询模式,中断模式实时性能好,适合于紧急情况,中断次数多,中断任务切换频繁影响主要任务的运行;定时查询模式,由于STl6C654具有缓存,定时查询方式具备一般实时性,数据不丢失。

1.2 系统组成

电路设计需要注意:1)MPC2860采用大端(big-end)工作模式,STl6C654从BD0开始接收数据。STl6C654数据总线D[0..7]连接MPC860的数据总线D[7..0],地址总线A[O..4]连接MPVC860地址总线A[31..27];2)STl6C654采用Motorola模式即 接地,此时控制

接地,此时控制 为0,就是对4路串口同时使能,选择A3,A4就可以对具体通道 *** 作;3)采用定时查询模式,STl6C654的

为0,就是对4路串口同时使能,选择A3,A4就可以对具体通道 *** 作;3)采用定时查询模式,STl6C654的 与MPC860的

与MPC860的

连接, 与MPC860的

与MPC860的 连接,

连接, 置空,以实现了串口数据的接收后以UDP协议包发送到以太网和从以太网收到的UDP包数据按协议重打包后发送到指定端口;4)时钟选择为14.7654MHz,

置空,以实现了串口数据的接收后以UDP协议包发送到以太网和从以太网收到的UDP包数据按协议重打包后发送到指定端口;4)时钟选择为14.7654MHz, 为O,但实际波特率要通过MCRBIT7初始化设置,各路传输速率最高可达921.6 Kb/s。STl6C654电路设计如图3所示。

为O,但实际波特率要通过MCRBIT7初始化设置,各路传输速率最高可达921.6 Kb/s。STl6C654电路设计如图3所示。

2 系统软件设计

2.1 *** 作系统

Vxworks是由WRS(Wind River System Ine.)公司开发的一套具有微内核、高性能、可伸缩的实时 *** 作系统,支持广泛的网络通信协议,支持32位的C++PU,包括Intel公司的x86、MIatorola公司的68k和PoweerPC、MIPS、ARM,并能够根据用户的需求进行组合;同时WRS公司还提供了优秀的实时 *** 作系统开发工具Tornado。Tornado是一整套强有力的交叉开发工具,它能够支持几乎所有的工作平台和目标处理器,所提供有工具可用于所有目标机,并具有两种调试模式(系统模式和任务模式),能够轻松给Vxworks *** 作系统添加删除各种通信协议,能够支持目标机和宿主机的如以太网、串行线路、在线仿真等通信选项,其机制和功能都是基于C/C++语言,任务、中断、通信都提供了统一的API接口。这些特性为编写应用程序和设备驱动提供了极大便利。Tornado目前已发展到6.O及更高板本。本设计开发工具是Tornado 2.0。

在Vxworks下,设备驱动可以嵌入到内核随系统一起启动,也可以作为加载模块在系统启动后运行。前一种需要修改内核,需要熟悉内核结构和运行方式,这实现比较困难:而后一种比较简单,与编写一般的应用程度类似。本设计采用后者。

2.2 STl6C654程序设计

定义消息结构MSG_STRUCT和串口接收UART_RECE_STRUCT数据结构:

系统启用收发2个任务,初始化STl6C654后,实现收发数据流程如图4所示。

3 结论

在详细分析MPC860和STl6C654元件性能参数的基础上,介绍了具体的开发实例。硬件采用MPC860连接STl6C654,软件采用VxWorks系统,双任务驱动STl6C654进行串口收发通信,该实例已在TornadoⅡ2.0_2版本上通过调试,单通道连续收或发5字节实验,1秒20次无丢失包。该

实例已成功应用于某型网络设备开发中。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)