基于MPC860的HDLC通道驱动程序的设计与实现

摘 要: 阐述了MPC860芯片及其SCC接口的基本工作原理,介绍了在SCC通道上实现HDLC协议的基本设计思想及具体实现,并给出了主要功能函数的设计流程。

关键词: HDLC MPC860 VxWorks *** 作系统 驱动程序

HDLC作为一种基于点到点/多点的数据链路层协议,常常用来连接路由器和网关等网络设备。摩托罗拉公司生产的MPC860微处理器是当前应用非常广泛的嵌入式微处理器,良好的性价比和强大的通信与网络协议处理能力以及丰富的通信接口支持使其非常适合构建VOIP网关;特别是其SCC接口本身支持HDLC协议,因此可以通过它的一个SCC接口来为VOIP网关和信令网之间提供链路支持。VOIP作为一种基于IP的数据传输技术,广泛地利用Internet全球互连环境,将传统的PSTN电话网和Internet网络合二为一,因此可以有效地降低系统成本和管理成本。作为一种高效且经济的数据和话音通信方式,它是当前技术研究和开发的热点。实现VOIP的关键是IP网关,其中信令网关主要将信令网的信令信息转换成Internet网络的相关报文控制信息。本文介绍如何在MPC860板的SCC2通道上实现HDLC的驱动程序,从而为信令网和网关之间提供链路支持。

1 HDLC简介

HDLC是一个在同步网上传输数据并面向位的数据链路层协议,具有透明传输、可靠性高、传输效率高以及灵活性高等特点。它采用点对点或多点(多路播送或一对多)连接的主/从结构,要求每个从站都有唯一的地址,从站只有在允许通信时才能且只能和主站通信,这就消除了串行线路上由于几个从站同时发送引起冲突的可能性。其它的通用的二层协议如SS#7、AppleTalk、 LAPB、LAPD等都是基于HDLC及其帧结构的。HDLC帧结构如图1所示。

F:标志位,每个HDLC帧以8位序列(01111110)标志帧的开始和结束,这是HDLC中仅有的两个包含连续六个1的可能组合。为了避免在其它域中出现这种组合,HDLC采用了一种叫作位插入的办法实现组合,即每发现有连续五个1时便在下一位自动插入一个0,接收器在收到连续五个1之后又自动删去插入的0。标志位除了标志帧的开始和结束外,还可用作时钟同步,接收设备不断地搜寻标志位,以实现帧同步,从而保证接收部分对后续字段的正确识别。另外,在帧与帧的空载期间,可以连续发送这种标志序列,用作时间填充。

A:目的地址位,用于指示报文发往何站。每个从站必须有唯一的地址,主站必须知道每个从站的指定地址。全“1”构成的地址在HDLC中定义为广播地址,全“0”构成的地址在HDLC中定义为无站地址,用于测试数据链路的状态。

C:控制位,用于系统初始化、标志帧的序号,并在报文发送完成后通知从站响应,对以前发送帧进行应答。尾随控制段的信息通常用于报文传输、出错报告和其它各种功能,这些功能由控制段的格式完成。有三种格式可供使用:报文格式、监控格式和无序号格式。

I:信息域,是可选的。如果信息存在,它必须有8位整数数量的长度。

CRC:帧校验位,长度为16位或32位,帧校验序列用于对帧进行循环冗余校验,其校验范围从地址字段的第一比特到信息字段的最后一比特的序列,并且规定为了透明传输而插入的“0”不在校验范围内。

HDLC常被用来向X.25、ISDN和帧中继网等提供信令和控制数据链路。

2 MPC860及其SCC接口

MPC860是美国摩托罗拉公司生产的一种通用的32位嵌入式通信控制器。它是以RISC体系结构为基础并在片内集成有微处理器和多种外设接口的专用通信芯片,具有强大的通信和网络协议处理能力,可广泛应用于各种通信和网络产品中。它主要由嵌入式PowerPC内核、系统接口单元(SIU)和通信处理器模块(CPM)组成。它的CPM提供了丰富的串行通道,包括四个串行通信控制器(SCC)、两个串行管理单元(SMC)、一个串行外围接口(SPI)和一个I2C接口。

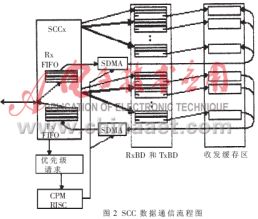

其中,SCC是MPC860最强大的通信设备。四个SCC端口通过相应的配置可支持不同的协议,如以太网、IEEE802.3 10M局域网、HDLC、appleTalk、通用异步收发协议UART、同步UART、串行红外线接口IrDA、二进制同步通信BISYNC及透明发送等网络协议,可以分别用于网桥、路由器、网关、LAN、WAN及专用网。因此,本文将其中的一个SCC端口配置成HDLC模式用在VOIP信令网关中,为信令网和网关之间提供链路支持。SCC数据通信基本流程如图2所示。

当处于接收状态时,数据首先进入FIFO。当接收FIFO充满时,CPM向SCC发请求,并由CPM RISC处理该请求,然后通过写SDMA将数据按照缓存描述符的指示存入指定的缓存中。缓存描述符是进行数据收发的基础,它由三个部分组成:头16个比特用来描述收发的状态模式;接下来是数据长度描述符,表示即将存入缓存的数据长度;最后是数据指针,它指向即将存入数据的缓存。发送过程与接收过程基本上是一样的,通过缓存描述符,能够正确读写缓存。

3 驱动程序的设计思想及其实现

这里选择VxWorks作为本CPU板的 *** 作系统。VxWorks是美国风河系统公司推出的一种高性能、可裁减的实时嵌入式 *** 作系统,以其良好的可靠性和卓越的实时性被广泛应用于通信、军事、航天等领域。因此,程序的设计必须按照这个 *** 作系统的结构来构建。本文的主要目的是将MPC860处理器的一个SCC通道配置成为HDLC模式,以支持VxWorks *** 作系统下的HDLC通信,所以程序的设计主要围绕这个目的进行,在此并没有按照传统驱动的模式构建驱动程序,而是直接对硬件进行 *** 作。首先设置通道参数,将其配置成HDLC模式,然后设计基本功能函数。当驱动程序运行时,首先要进行SCC通道的初始化以及存储区的初始化,然后才开始执行收发功能,在这当中要加上中断控制。按照这个程序的基本流程,具体的实现分为下面几步(在本设计中将SCC2配置成HDLC模式)。

3.1 定义参数RAM

参数RAM主要包括通道参数RAM和通道协议参数RAM两部分,SCC通道的主要参数都在这个里面配置。它们包含CPM RISC用来正确 *** 作SCC通道的特定协议所用的信息。

3.2 初始化SCC2

(1)将MPC860的PA12、PA13引脚作为SCC2的收发引脚。

(2)MPC860有四个BGR和八个外部时钟引脚,将SCC的收发时钟分别配置成内部时钟和外部时钟。

(3)将SCC2配置为NMSI模式。

(4)初始化SDCR寄存器,给予SDMA一个仲裁ID以提供U总线上的优先级。

(5)初始化SCC2的参数RAM(这步对所有的协议都是通用的):

①设置Rx/TxBD 表的基址相对于双端口RAM的偏移量;

②设置收发缓冲区描述符表基址相对于IMMR寄存器中值的偏移量;

③设置Rx/Tx 的函数代码;

④在MRBLR中设置接收缓存的最大空间。

(6)针对SCC2的HDLC模式进行初始化;

①通过C_MASK和C_PRES 设置CCITT-CRC;

②对CPM维护的五个计数器DISFC、CRCEC、 ABTSC、 NMARC和RETRC清零;

③在MFLR中定义最大帧长度,通常定义为0x0100,表示最大帧长度为256字节;

④在RFTHR中定义接收到多少个HDLC帧时产生一个中断申请,当将RFTHR置位0x0001时,表示每接收到一个帧产生一个中断申请;

⑤设置接收地址,hmask用来定义地址掩码,当hmsk=0x0000时,表示接收所有帧。

每个SCC有四个地址存储器HADDR1~HADDR4,所以每个SCC可识别四个地址,包括广播地址。接收时,通过与HDLC帧的目的地址进行比较,确定接收该帧还是丢弃。

3.3 初始化收发缓存区描述符

(1)在初始化缓存区描述符的过程中,收发都必须停止。通过将GSMR_L2的ENT和ENR置零,然后配置CPCR中的CP命令就可以禁止收发。

(2)配置收发缓存区描述符:

①配置当前接收缓存区描述符表的基地址,即IMMR的基地址再加上收发缓存区描述符表相对于IMMR的偏移地址。由于发送缓存区描述符表紧跟在接收缓存区描述符表的后面,因此发送缓存区描述符表的基地址为接收缓存区描述符表的基地址加上整个接收缓存区描述符表的长度。

②初始化发送缓存区描述符表和接收缓存区描述符表。如果收发缓存区都为空,分别将每一个发送缓存区描述符表和接收缓存区描述符表的状态模式参数中的状态位E置1、数据长度置0,并将它们的地址设置成相应的值。如果收缓存区或发缓存区不为空,则应该先将这些缓存区清零。值得注意的是,最后一个收发缓存区描述符表的W位必须置1。

(3)初始化完成后,应该将ENT和ENR位置1。

3.4 收发功能的实现

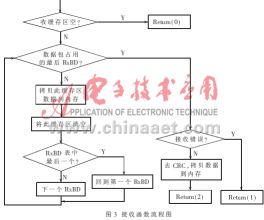

3.4.1 接收函数

接收函数流程图如图3所示。

在GSMR_L2寄存器的ENR位置1的前提下,HDLC控制器进入接收允许状态。在正式读入数据前,必须先检测帧开始标志,并匹配地址,然后决定是否进入接收状态。进入接收状态后,首先提取RxBD的状态模式字节,若接收未准备好,则继续等待,若准备好了,则开始接收。由于一个数据包可以放置于多个缓存,所以检测RxBD状态模式字节的L位,以判断是否为本帧的最后一个缓存:如果不是,则关闭这个缓存,处理下一个缓存描述字;如果是,接收完最后一个缓存的数据后结束接收过程。对于最后一个buffer,需要检测是否有接收错误。

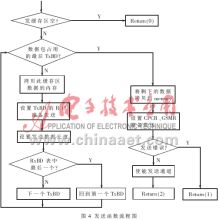

3.4.2 发送函数

发送函数流程图如图4所示。

在GSMR_L2寄存器的ENT位置1的前提下,HDLC控制器进入发送允许状态。首先提取TxBD的状态模式字节,若发送未准备好,则继续等待,若准备好了,则进入发送状态,在发送数据中间插入适当的标志位后就可以发送。由于一个发送数据包可以包含多个缓存,所以检测TxBD状态模式字节的L位,以判断是否为最后一个缓存:如果不是,则关闭这个缓存,处理下一个缓存描述字;如果是,控制器进入关闭发送状态。对于最后一个buffer,需要做两件事情:(1)检测是否有发送错误。(2)以剩下的实际数据长度作为发送帧中数据段的长度发送出去。

3.5 中断处理

在这个驱动程序中,只处理SCC2产生的中断。首先确定是否是CPM产生的中断,然后读取寄存器CPM中断向量寄存器(CIVR)的VN字段判断是否为SCC2产生的中断。如果是的话,就读取SCEE确定中断类型,然后做出相应的处理。

本程序通过在MPC860上做环回测试,情况良好。但在程序实现过程中,中断的控制还有待于进一步完善。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)