1 综合优化设计的一般流程和方法

在FPGA处理器没有选定前,可以进行SOPC系统的开发。根据编译和优化的效果指导处理器芯片的选型,选择合适的处理器型号、速度等级和封装。当硬件系统设计好后,就只能在已选择好的处理器芯片上进行优化。一般的优化方法有Verilog程序代码优化、编译和布线优化设置,在添加Nios II系统后也涉及对Nios II系统的优化。在设计过程中应遵循模块化设计思想,如果前面的优化都不能达到满意的效果,则需要使用逻辑锁定技术和应用DSE算法进行优化。

2 综合优化设计策略

2.1 Quartus II软件优化设置

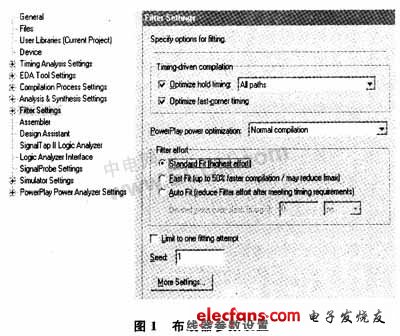

在进行综合前,对软件编译和布线进行优化设置是优化设计的一个重要步骤,不同设置对综合布线的结果有较大影响。几个比较重要的设置包括时间要求设置、编译器设置,最重要的是布线器的设置,如图1所示。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)