本文采用脉冲多普勒、数字波束形成等技术,为某型雷达导引头信号项目设计了其关键部分——雷达数字信号处理机。本处理器采用FP GA平台实现,文中详细介绍了该处理器基于FPGA的基频信号产生模块、回波信号采集模块、控制信号产生模块和时钟模块等硬件模块的设计思路。

1 系统方案设计

目前,主要采用三种方法实现雷达数字信号处理系统设计:基于DSP技术实现雷达数字信号处理,基于“FPGA+DSP”技术实现和基于FPG A技术来实现。本方案选用Xilinx Virtex4 FPGA XC4VSX55,其属于Xilinx SX系列,专用于高速数字信号处理领域,FPGA非常适合于高速数据的采集控制、高速数据传输控制,且目前的主流FPGA均含有硬件乘加器、大量的逻辑单元、流水线处理技术等硬件结构,可高速完成FFT、FIR、复数乘加、卷积、三角函数以及矩阵运算等数字信号处理。高端FPGA更是含有大量的DSP单元、RAM单元、MGT高速传输单元、DDRII数据控制器等IP核,这些均是实现高速实时数字处理的重要资源。此外,FPGA编程灵活,易于升级。其高度集成性和高灵活性使对外部硬件的需要更少,额外的硬件开销大大减小,非常适用于雷达数字信号的处理和将来的算法升级。因此本方案采用FPGA技术进行雷达信号的处理。

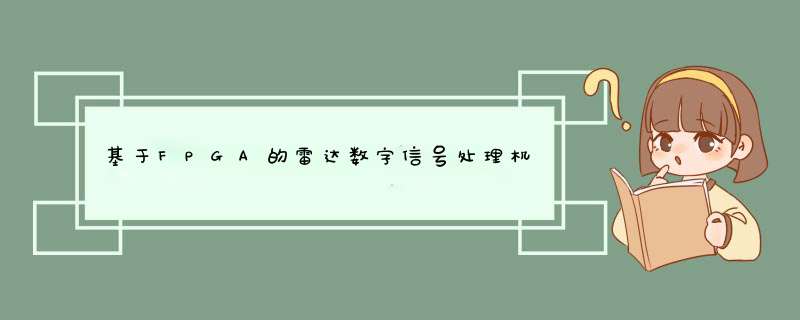

根据项目的设计需求,设计的雷达数字信号处理机系统整体框图如图1所示。

输入调理电路对接收到的回波信号进行预处理,预处理过后的信号经ADC转换为数字信号;采样后的信号经频率搬移,将100MHz的中频信号搬移到20MHz,然后对6个通道的信号进行幅度校正,消除通道间的不平衡问题。校正后的6路信号分别与两个正交本振信号相乘,进行数字混频,完成信号的正交分解,得到12路I/Q正交信号。12路I/Q信号与预先设置的权值进行加权计算并进行累加,完成数字波束形成(DBF),得到一路合成信号;通过FIR低通滤波器,对数字波束合成后的信号进行数字滤波,滤除30 MHz以上的谐波信号;由于发射信号采用了伪码调相技术,所以对DBF后的信号依照发射信号的m序列进行伪码解调(即对回波信号进行相位变换),完成回波信号的解码。对滤波后的信号进行相参累积,累积次数达到设定值后,进行FFT变换;FFT结果与检测门限进行比较,当发现回波信号特征时,给出回波的通道号和频率,并给出启动信号。

2 系统实现

2.1 硬件设计

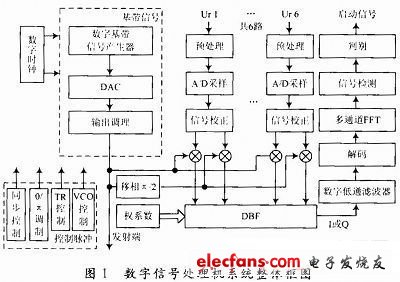

结合系统需求和系统总体设计,本系统的硬件主要包括A/D采样部分、D/A输出部分、控制信号输出部分、时钟部分、FPGA设计及配置、电源管理等六大部分,总体框图如2图所示。各功能模块介绍如下:

(1)A/D采样部分

根据性能指标,系统外接6路模拟信号,信号频率为100MHz,输入信号幅度为±1 V,幅度分辨率为0.5 mV。因此设计了两片A/D转换模块ADS6444实现带通欠采样,单片ADS6444支持4通道模/数转换,最高采样频率为105 MHz,采样位数为14 b的高性能A/D转换电路,输入信号量程为2 VPP,幅度分辨率为0.12 mV。配合前端数据调理芯片THS4513,能满足系统对采样电路的需求。

(2)D/A转换电路

无论是调频连续波或脉冲多普勒调制方式,均需要对外输出100MHz的基频信号,因此设计了D/A转换电路。D/A转换芯片采用MAX5887,它是14位、500 MSPS数模转换器(DAC),工作电压为3.3 V,提供76 dBc的无杂散动态范围(SFDR)(fout=30 MHz时)。该DAC支持500MSPS的更新速率,且功耗小于230mW。

(3)控制信号输出部分

(4)时钟部分

数/模转换部分、模/数转换部分、FPGA正常工作均需要低抖、高稳定性的时钟,在此使用专用时钟芯片AD9517来产生系统需要的各个时钟。AD9517是一款集成高频时钟发生器,具有如下特点:低相位噪声、VCO频率变化范围为1.75~2.25 GHz,4路LVPECL时钟扇出,输出频率范围为50 MHz~1.6 GHz可调,4路LVDS时钟扇出,输出频率范围为25~800 MHz可调,4路LVDS时钟扇出可设置为8路CMOS时钟扇出,且相位可调、可串行控制。

(5)FPGA设计

FPGA要完成对A/D采样数据的数据处理、D/A转换的数据输出、控制信号的产生、核心算法的实现、USB调试接口的数据输入/输出等,是整个系统设计的重要部分。根据系统需求分析,使用了Xilinx Virtex4SX55。Virtex4 SX55含有512个DSP处理单元,具有强大的数据处理能力,能够满足本系统的信号处理需求。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)