在一些军用芯片的早期设计中,一般先采用比较成熟的商用协议芯片进行军用化改造(通常做成板卡形式),而商用芯片的军用化改造主要体现在确定性、实时性、稳定性、安全性等问题上,所以一般需要在商用协议芯片的上层加入较多的控制功能。FPGA以其资源丰富,易于组织流水和并行处理等优点,为这种复杂控制提供了很好的选择。而SPI在芯片的管脚上只占用四根线,节约了芯片的管脚,同时为PCB的布局上节省空间,因此在基于FPGA的读写接口设计中,高速SPI是一种很好的选择。

1 SPI结构

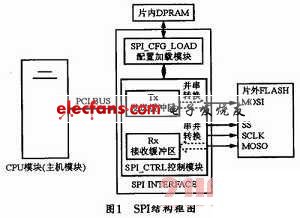

SPI (Serial Peripheral Interface-串行外围设备接口)是Motorola公司推出的一种高效率全双工同步串行数据接口,以主从模式工作,广泛应用于FLASH,实时时钟,AD转换器等。SPI串行外围设备总线根据串行同步时钟极性(CPOL)和时钟相位(CPHA)两个参数的设置分为四种工作方式(SPO,SP1,SP2,SP3)。本板卡选用的片外存储器AT25F1024仅支持0和3模式,为简化设计,本设计的SPI时钟采用SP0模式(CP-OL=0,CPHA=0),时钟极性为低电平,时钟相位串行时钟上升沿采样数据,下降沿数据输出.SPI为主从工作方式,主设备由三部分构成,SPI_CFG_LOAD配置加载模块可自动读取存储器FLASH的值,并加载到片内DPRAM中。主机通过配置SPI_CTRL控制模块相应的寄存器,来完成对片外FLASH的访问。SPI结构框图如图1所示。

2 高速SPI接口设计

2.1 配置加载模块的设计

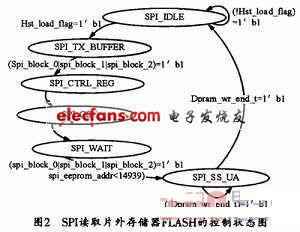

SPI_CFG_LOAD配置加载模块主要完成从片外FLASH读取数据,并将数据存入片内DPRAM中的功能。图2给出了对应的状态机设计。

各状态说明如下:

SPI_IDLE:空闲状态,如果主机配置了寄存器SPICFGSTART,状态就跳到SPI_TX_BUFFER状态。

SPI_TX_BUFFER:在此状态主要向SPI_CTRL模块的发送缓冲区地址0填入8位读命令及读取数据的三字节起始地址,状态机之间进入下一状态。

SPI_CTRL_REG:在这一状态,配置SPI_CTRL模块CTRL寄存器的值,包括一次读 *** 作搬运的数据位数,数据加载方式。如果配置GO位为“1”,表明可以开始进行读传输,进入下一状态SPI_CS。

SPI_CS:配置SPI_CTRL)模块寄存器SS位的值,以选择传输数据的从设备。

SPI_WAIT:本状态判断读 *** 作的起始地址和终止地址是否在要求的范围内,如果处于相应的范围,地址自动加64后,状态机进入SPI_SS_ UA状态。

SPI_SS_UA:等待片内DPRAM的写 *** 作完成,如果DPRAM_WR_END_T信号为高,说明当前的传输 *** 作已经结束,可以进入下一次的访问,状态机进入SPI_IDLE状态。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)