可穿戴电子设备对设计工程师提出了前所未有的挑战—设计工程师需要在没有专用芯片组或标准化架构的情况下创建智能、紧凑和多功能的产品。由于专用芯片组(标准化架构)的缺失,设计工程师需要在可穿戴产品中使用为移动和手持应用设计的器件和互连技术。

如何在两个不相关的器件之间实现数字与模拟“鸿沟”的桥接是一个不小的设计挑战,而这对于有严格空间和功耗限制的可穿戴设备来说更是难上加难。同时,发展迅速的市场要求设计工程师紧跟消费者不断变化的需求,快速升级现有产品的功能并推出全新的产品。

本文将针对可穿戴产品的设计挑战进行研究,并将探索如何使用可编程逻辑产品来解决这些问题。文章相关的设计实例旨在说明如何将专用可编程器件应用于以下三个方面:

扩展。使用额外的逻辑和定制功能扩展现有ASIC和ASSP的功能和使用寿命。

升级。使用可编程逻辑产品实现新协议和标准,并通过桥接实现互不兼容元器件间的互连,以此升级可穿戴设备的设计。

创新。无需为ASIC开发投入大量时间和费用,使用可编程逻辑产品提供的灵活平台来实现高级功能或全新的特性。

可穿戴设备带来前所未有的设计挑战

可穿戴电子产品正处于发展早期,技术尚未成熟,就像地球上的生命进化过程一样,将发生像寒武纪生命大爆发一样百花齐放的技术创新。可以预见至少在未来的3到5年内将不断有各种各样的产品和试作面世,形成具备以下特征的市场:

●市场快速创新,而消费者的需求也以同样的速度快速变化;

●全新类型的产品出现和发展,有时候也会最终消失;

●出现众多相互竞争的产品,但未能形成标准的功能集;

●即使有也只有很少的标准化架构或接口标准。

在这段蓬勃发展的时期里,产品依托的半导体器件的发展将跟不上产品本身迭代更新的速度。由于IC开发通常需要12至18个月,如果制造商坚持为可穿戴市场开发ASIC,很可能导致产品上市时功能并不尽如人意或已然过时。

没有专为应用优化的微控制器(MCU)和ASSP,可穿戴设备设计工程师就必须使用通用的MCU或使用来自更成熟应用的高度集成器件,如来自智能手机、平板电脑以及其他手持/移动设备中的器件。上述这两种方式都为设计工程师提供了高集成度的嵌入式计算平台,无需为开发专用器件投入大量的时间和成本。不仅如此,很多开发工具和应用软件都支持大多数这些现成器件,这也是额外的优势。

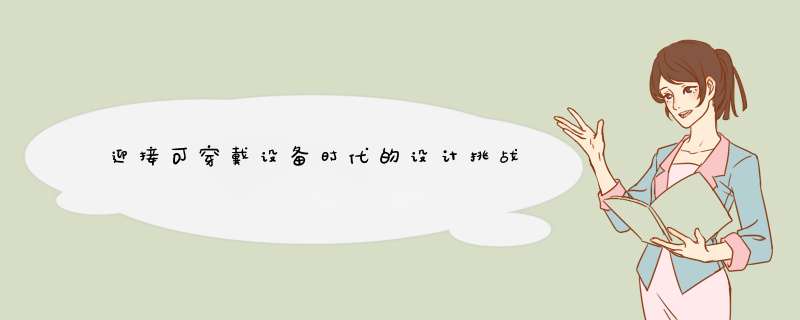

第二个挑战,也正是更普遍的问题—大部分这些嵌入式计算器件并不具备相关接口用于可穿戴应用中最常用的各类传感器、显示屏和其他I/O器件。在某些情况下,传感器或显示屏的接口不匹配系统的数据总线,或不兼容系统应用处理器使用的格式,这将导致“数字断裂(DigitalDisconnect)”的发生(图1)。

图1:“数字断裂”常见于大多数CMOS图像传感器的LVDS接口和许多常用应用处理器使用的CSI-2I/O总线之间

例如,常用于CMOS图像传感器的Sub-LVDS接口采用与许多常用应用处理器使用的CSI-2接口不同的数据帧格式(图1)。此外,器件的接口还可能具备不同数量的串行通道。另一个导致“数字断裂”的原因是,许多通用MCU具备GPIO以及其他并行接口,其必须要转换成一种现在大多数传感器和显示屏使用的串行格式。此外,可穿戴应用中采用的紧凑封装MCU的引脚数量太少,限制了其可直接访问的器件数量。

应用处理器所支持的接口与众多传感器和输出设备所要求的接口之间也存在着“功能性鸿沟”。一个简单的例子是,可穿戴设备可实现电视机或其他电子产品的红外远程控制。而这种情况下,大多数MCU并不具备的LED驱动能力成为了应用处理器和红外(IR)LED之间的“功能性鸿沟”。

IR编码器是一种纯数字功能,至少从理论上来说可以由MCU的应用处理器实现。但是在许多情况中,这并不是最理想的解决方案,因为实时编码需要占用的处理器资源已经超过了系统能够节省的资源。并且,应用处理器在编码任务上花费的额外时间将导致消耗过多有限的系统功耗,因此最好使用硬件实现。

基于FPGA的解决方案

现在,FPGA可提供高性价比的方式来实现接口间的桥接以及为现有的器件添加新功能并缩短设计周期。而早期的可编程逻辑器件相对来说过于昂贵,并且功耗惊人,所以常用来作为初代设计或小批量产品的原型设计工具和“胶合”元件。

步入21世纪后,深亚微米工艺和新架构的发展带动了性能和通用性增强的新型FPGA的实现,并显着降低了成本和功耗。这使得现在的FPGA能够在可穿戴电子设备中发挥多种作用。

当然,FPGA仍在其传统的应用领域中不断发挥作用,如提供“胶合”逻辑、实现基础功能,包括提供额外的逻辑单元(门电路、锁存器、触发器等),添加输入信号调节(电平转换、施密特触发器和反相器),以及为已有的主机处理器I/O互连提供扩展路径。

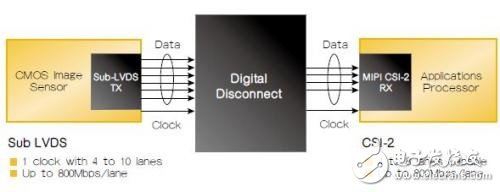

FPGA还能用于实现前文所提到的更复杂的功能。其最简单的形式是提供桥接功能,如图2所示,FPGA能解决图1中展示的传感器Sub-LVDS接口与应用处理器的CSI-2I/O总线之间的桥接问题。

图2:嵌入式图像传感器和应用处理器间的桥接

在串/并转换应用中也经常使用基于FPGA的桥接。图3展示了可编程逻辑器件是怎样将应用处理器的标准并行总线转换成现在的可穿戴设备显示屏最常用的MIPIDSI接口的串行格式的。在该应用中,FPGA负责实现以下功能:

重新定义图像传感器的LVDS输出格式,以匹配应用处理器支持的通道数量和数据速率;

将传感器的数据时钟信号传输至应用处理器,实现任何所需的信号编码;

使用可编程逻辑而不是应用处理器有限的机器周期来实现屏幕刷新动作。

图3:用于可穿戴设备显示屏的GPIO/DSI桥接

桥接功能也可用作基于FPGA的更大系统元件的构建模块,如实现图4中的双输入桥接/处理器,它将接收来自2个独立图像传感器的CSI-2串行数据流,并将其处理为单个CSI-2或并行或HiSPI输出。根据所选的算法,可对独立的数据流进行色彩调整或在时间或空间上进行补偿生成单幅3D图像,或在屏幕坐标空间的不同位置对其单独显示产生画中画效果。

图4:FPGA可用于实现实时视频处理功能,如生成3D立体图像、视场或画中画

FPGA助力节能技术

在前面的几个例子中,设计的主要目的是为了增强应用处理器本身的互连或功能。但这些基于FPGA的解决方案还提供了另一个重要的好处:使得MCU或ASSP无需同时执行一个或多个计算密集型任务,从而节省了有限的处理器资源。

但是,在许多情况下,这些设计的功耗降低具有更重要的意义。例如,图3中的设计包含了一个硬件屏幕刷新功能,其仅需消耗传统处理器内核所需功率的一小部分。同样,图4中的一些小尺寸、低功耗FPGA逻辑器件独立于主机处理器执行图像处理任务,这使得主机处理器大部分时间可处于节能睡眠模式。

下面探讨的许多应用都使用这种节能设计方法,适用于大多数有低功耗需求的可穿戴应用。

FPGA可加速设计升级和新设计实现

可穿戴电子设备发展迅速,每一代新产品都比上一代添加了更多的功能和特性。在这些应用中,小尺寸、低成本的FPGA经常被用来扩展可穿戴式设备应用处理器的基本功能。

许多现代的微控制器都有强大的计算能力来管理传感器和处理其产生的数据,并将它与其他数据流进行整合。但使用微控制器来完成这些工作会占用宝贵的I/O资源,并要求处理器长时间处于工作状态,从而会影响电池寿命。

而FPGA可以用来创建半自主的I/O模块,能够从多个传感器收集数据,并在没有处理器干预的情况下完成其他高级功能。“永远在线”的低功耗计步器采用3轴加速度计作为主要传感器,记录佩戴者的步数,计算所走的距离并测定燃烧的卡路里以及运动时间。

在该设计中,一些FPGA逻辑单元被配置用作加速度计的I2C接口和应用处理器SPI/O总线之间的桥接。其他的FPGA功能块用于配置和管理加速度计。可编程逻辑也可以用于处理原始的加速度计数据,针对带有噪声的数据流采用统计学滤波和步数检测算法。FPGA的另一部分功能是用来缓存得到的步数和加速度信息,直到主机处理器从低功耗睡眠状态唤醒并收集这些数据。采用可编程逻辑内核来执行这些计算密集型任务,可使应用处理器长时间处于睡眠模式,从而有助于减少计步器的功耗。通过FPGA实现这些功能也使设计人员能够在不影响计步器的性能和精度的情况下,使用更简单、更低功耗的微控制器。

FPGA提供可扩展的解决方案

采用FPGA的另一个优点是,FPGA厂商通常会提供一系列类似的器件,每个器件有不同的可编程逻辑和I/O组合。使用FPGA作为ASIC的补充或替代,设计工程师可以选择他们目前所需的逻辑门数量,开发大小合适的解决方案。

由于同一FPGA系列的器件共享参数、特性和开发资源,各种逻辑密度和I/O配置选择使得制造商可以采取“升级时再购买”的策略,为现有的设计添加新的功能,或重组现有的功能开发新的产品。由于同一系列器件共享通用的工具链和IP库,设计工程师可以迅速将升级和后续设计从设想变为产品推向市场。

总结

可穿戴设备的标准架构、功能集和专用芯片的缺失为本来就面临紧张成本、功耗和尺寸约束的移动消费电子设计带来了许多前所未有的挑战。本文介绍了FPGA能够通过一些简单的方法帮助设计工程师解决上述问题,例如:为现有微控制器、传感器、显示器等之间的接口桥接,为现有的微控制器和ASSP添加新的互连和功能,以及在某些情况下提供了一种替代ASIC或SoC的选择。

由于其灵活性、可扩展性和较低的解决方案成本,FPGA为许多类型的产品重新定义了传统的设计周期,为设计工程师提供了许多超越传统ASIC的优点。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)