数据链路层包括发送和接收两个部分,本章主要介绍数据流从进入到发射器的数据链路层到从接收器的数据链路层出来的所经过的具体处理过程以及涉及到的模块。

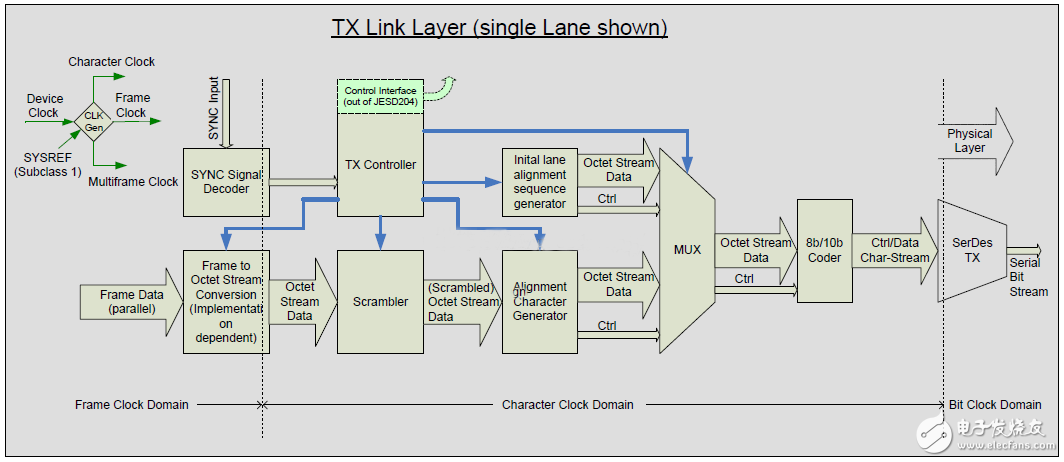

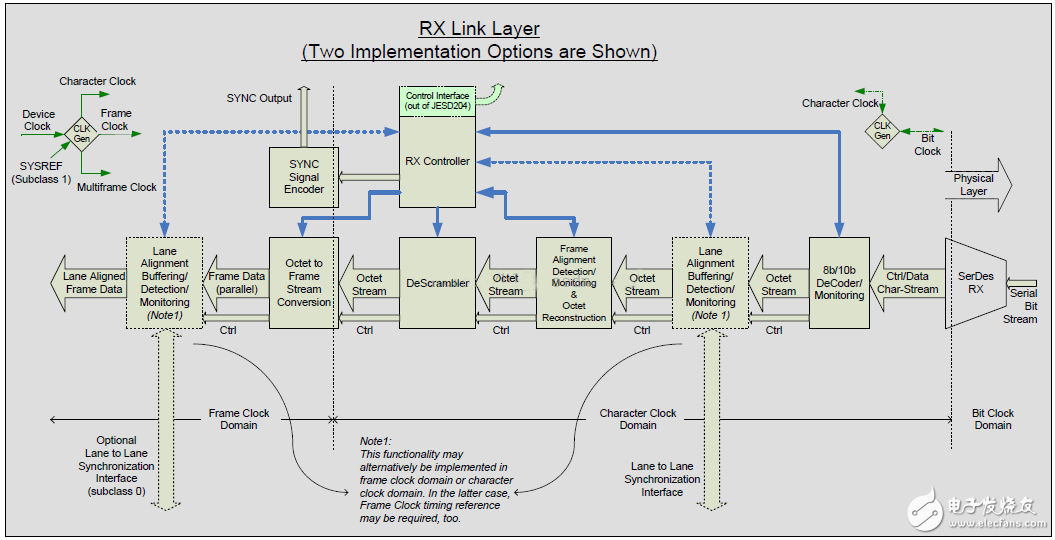

下面的图21和图22分别是发送数据链路层和接收数据链路层的内部结构图,本章节将从发送链路层开始介绍每一个具体模块的功能,同时由于接收链路层中包含的模块总是发送的模块的功能是相对的,所以在介绍发送链路层中的模块时,将同时介绍接收部分模块的功能。

进入链路层的数据是在传输层映射为数据帧的,进入数据链路层的数据以帧为最小单元,而数据链路层工作在charcter clock时钟域,所以在进入数据链路层后,farme data 将先经过Frame_to_octet模块,Frame_to_octet模块将输入的数据帧转换成octet的数据流。

数据流在Scrambler模块将进行加扰处,加扰的功能是可选择的。

经过加扰处理的数据流经过alignment_character_generator模块将进行字节替换,字节替换的目的是为了检测数据通道数据流是否工作正常。

Mux模块通过TX_controller模块选择需要数据的数据流

数据流在8b/10bcoder模块中将进行编码 *** 作,并最终输出到serdes_tx模块。

TX_contrller 为数据链路层的控制模块,该模块通过control interface与上层接口交互控制信息,并对控制信息进行解析,进而控制数据链路层的工作流程。

IniTIal_lane_alignment_sequcence_generator是不同数据通道间的同步序列的生成模块,该模块将在系统启动同步后,产生所需要的同步序列。

图21:数据链路层发送器的内部结构图

在接收器部分,数据链路层的数据流的具体 *** 作如下:

物理层的serdes模块将输入的1bit的串行数据流转换为10bit并行数据流,并通过特殊的对齐字节完成数据流的对齐,并将对齐完后的数据通过8b/10b进行解码,并出输出8bit位宽的octet数据流。

解码输出的数据流将通过lane_alignment_buffering_detecTIon_monitoring模块,该模块将通过对校准字符在数据帧中的位置,来判断现阶段的数据传输不同通道间是否同步。

接下来数据流经过Frame_alignment_detecTIon_monitoring模块,该模块也是通过对校准字符在数据帧中的检测来数据帧是否发生对齐的错误。

在经过两级的对齐检测后,数据将进入descrambler模块进行数据的解扰。

解扰后的数据流将通过octet_to_frame模块从新组合成数据帧,传输到数据传输层。

图22:数据链路层接收射器的内部结构图

以上便是系统中数据链路层对数据流的控制和处理流程,SystemC的模型中,上述的每一个模块将有相对应的模型,并且SystemC中模块的名字将与上述图中的模块名称保持一致。

1.1 RX ControllerRxcontroller作为数据链路成的控制核心,其内部需要完成的工作主要为两个方面,一方面通过数据接口与上层进行控制数据交换,一方面完成数据链路层的工作状态控制,本章将系统的介绍数据链路层的工作状态控制。

在Rx controller内需要完成的工作包括:code group synchronizaTIon、initial frame synchronization,这两部分表现为两个状态机的控制,完成数据流的同步和数据帧的同步。

1.1.1 code group synchronizationcode group synchronization的功能在系统上电或者要求系统从新同步时完成数据流的同步,该同步的具体的过程是在serdes的CDR模块中实现的,完成1bit数据流到10bit的串行转换。具体的同步细节如下:

在同步要求开始后,接收控制器发送同步请求,此时SYNC信号将保持低电平,发射器在接收到同步请求后,将会发送comma码:/K/=/K28.5/

接收控制器在接收以下的情况下降释放同步请求:

Subclass 0 devcies:在接收到4个有效的K码后,在任何数据帧的边界释放同步请求。

Subclass 1和Subclass 2:在接收到4个有效的k码后,在数据的复帧(mutliframe)的边界释放同步请求,也就是将SYNC信号拉高。

在接收到另外4个有效的comma码后,系统将认为数据code group synchronization完成。

当接收到一个无效的数据时,状态机将进入检测模式。

如果在检测模式中,累积收到3个无效数据时,认为系统未同步。

在检测模式中,如果检测到4个正确数据后会认为系统同步正常。

同步请求由接收器通过SYNC信号传输到发送器,并且SYNC低电平有效,SYNC信号只有在frame clock 的上升沿才会发送变化,但是也分两种情况:

Subclass 0:任何frame clock的上升沿

Subclass 1和Subclass 2:任何frame clock 和multiframe clock对齐的上升沿。

SYNC信号的低电平持续时间必须大于5个数据帧或者9个octet的持续时间。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)