**这篇文章是模拟接线 (Analog Wire) 内月度RF采样博客系列中的第8篇博文**

你认为你的射频 (RF) 采样设计运行的还不错,其原因在于你选择了合适的器件,并且定义了时钟源。不过先等一等;你所要完成的工作还远非如此。在不进行适当的频率规划,以确保谐波或时钟混合杂散中产生出洁净频谱的情况下,即使是最好的器件也会造成性能下降。我在上一篇博文中讨论了与交错转换器有关的某些缺陷。频率规划始终是良好收发器设计的一部分,不过RF采样更加关键,这是因为信号一直处于所需的频率频带范围内。与其它具有中间频率 (IF) 或基频级 (BB) 的配置不同,RF采样架构不具有清洁频谱的窄频带通道滤波功能。

在这些发射器中,管理要求将严格限制杂散乘积的等级,使其落在所需频带内,并且刚好在频带外。这些转换器内产生的杂散乘积在到达功率放大器 (PA) 之前无法被有效过滤掉。一旦受到辐射,这些乘积就有可能干扰其它用户。

用一个RF采样数模转换器 (DAC) 进行的频率规划确保了折返回第一那奎斯特区域内的谐波含量不在所需频带之内,或者在其附近。针对指定应用的频带是固定的;它是不可调节的,不过你可以调节转换器的采样率。增加采样速率可以生成一个更大的那奎斯特区域;然而,这并不能确保一个最优方案。

发射器频率规划示例

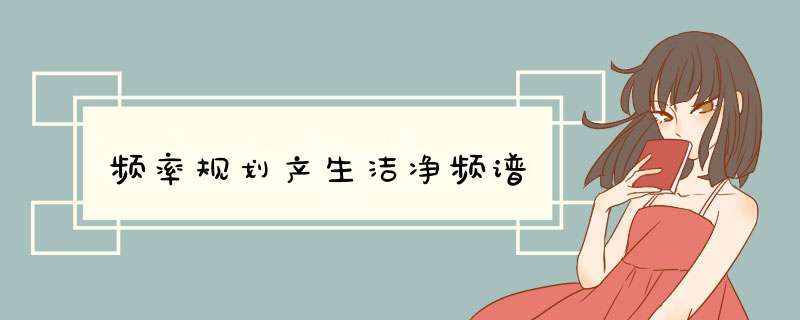

我们来看一个发射器示例,它的运行频率为2.14GHz,信号宽度为60MHz。图1显示的是具有8024MHz高频时钟速率的第一那奎斯特区域频谱。在这个速率下,所需要的频带(用蓝色标出)很清楚,但是第三和第四阶谐波,以及已知的杂散(用黄色标出)位于所需的频带附近。这些杂散积很难被过滤掉。

图1b显示的是同一频率,不过时钟速率减少为5683.2MHz。在这个时钟速率下,高阶谐波或者时钟混合杂散都不会位于所需频带的附近。在这个示例中,较低采样率方法比较适用,这是因为你可以轻松地将高阶杂散滤除掉。

图1:时钟频率为8024MHz (a) 和5683.2MHz (b) 时的频谱图

接收器频率规划示例

对于接收器来说,频率规划目标稍微不同。源自带内和带外信号的干扰会严重影响接收器的灵敏度。通过在RF输入端上进行适当的限带滤波,你可以最大限度地降低其它用户信号或发射器干扰所形成的带外干扰源。你无法过滤掉带内干扰源。频率规划确保来自带内干扰源的谐波含量不会折返回所需频带的内部。与发射器的情况不同,恰恰折返回频带外部的谐波含量不是一个问题。

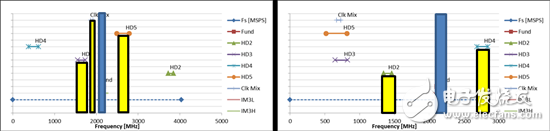

图2显示的是一个100MHz宽的信号,在中央频率为1950MHz的频带范围内运行。时钟频率为6144MHz。在这个配置中,所有这些较高阶谐波都位于频带外部。第二和第四谐波很接近,但是不在频带内部。这是一个传统低IF架构所不能比拟的。使用同样信号带宽运行的较低采样率模数转换器 (ADC) 无法实现一个干净的频谱,这是因为折返谐波覆盖了整个那奎斯特区域。

图2:时钟频率为6144MHz,中央频率1950MHz频带范围内,频带宽度为100MHz时的频谱图

你可以修改时钟频率来在所需频率发生变化时保持一个洁净频谱。在使用传统架构时,对于频率规划的调整需要你修改合成器和IF或基带滤波器级。只需调节采样率,RF采样架构就可实现简单频率规划调整。由于在不同频带下运行只需要对时钟频率进行调节,RF采样架构可以很轻松地适应不同频带和应用的要求。

下个月,我将讨论针对RF采样ADC的定时要求。请在下方给我们留言,告诉我们你在RF采样转换器设计方面还希望了解到哪些内容。

其它资源

在TI数据转换器学习中心内进一步了解与数据转换器有关的设计工作。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)