最近在做Spartan6上的视频输出,输出的接口是HDMI接口,要求格式是720P。

系统的时钟主要有

1. 750M(TMDS输出的IO输出时钟,必须接bufpll)

2. 75M(720P的像素时钟)

3. 150M

4. 100M (系统时钟)

5. 24M (外围设备需要的时钟)

工具是ISE12.2

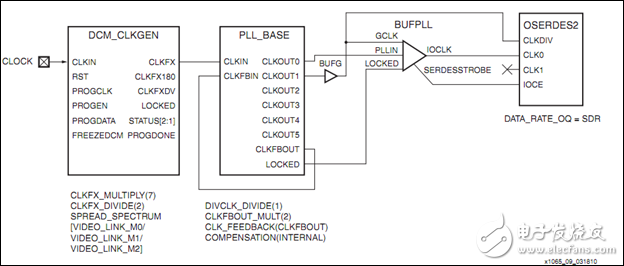

然后通过ISE自带的Clock_wizard来生成需要的时钟,750M是专门用来做TMDS的IO输出时钟,主要端口定义如下:

--Clock_gen是通过Clock_wizard自动生成的。

Clock_gen_inst : clock_gen

port map(

CLK_IN1 => sys_clk_in,

RESET => sys_rst,

LOCKED => LOCKED,

CLK_OUT1 => pix_clkx10_pll, --750M, need bufpll as buffer

CLK_OUT2 => pix_clk_pll, --75M

CLK_OUT3 => pix_clkx2_pll, --150M

CLK_OUT4 => sys_clk, --93.75M

CLK_OUT5 => external_clk_buf );

而pix_clkx10_pll必须添加bufpll

BUFPLL #(

.DIVIDE(5)

)

tx_bufpll_inst(

.IOCLK(tx_clkx10),

.LOCKED(LOCKED),

.LOCK(LOCK),

.PLLIN(pix_clkx10),

.GCLK(pix_clkx2),

.SERDESSTROBE(tx_serdesstrobe));

按照上面的时钟定义在mapping的时候出现这样的error:

ROR:Place - ConstraintResolved NO placeable site for U2/tx_bufpll_inst

ERROR:Place - SIO has over-constrained componet U2/tx_bufpll_inst to have to placeable sites. Constraints come from

driver constraints AND load IO constraints

Phase 4.2 IniTIal Placement for Architecture Specific Features (Checksum:fc8413ca) REAL TIme: 38 secs

Total REAL TIme to Placer compleTIon: 38 secs

Total CPU time to Placer completion: 38 secs

ERROR:Pack:1654 - The timing-driven placement phase encountered an error.

Mapping completed.

See MAP report file "hdmi_top_map.mrp" for details.

Problem encountered during the packing phase.

通过添加PLL或者删除其中一个clock,尝试了很多次还是报错。在网上找了,找到了类似的情况,但是没有给出解决方案来。

后来尝试添加约束才搞定的。直接指定bufpll的物理位置:

INST hdmi_encoder_0/hdmi_encoder_0/tx_bufpll_inst LOC= BUFPLL_X1Y5;

估计原因是:bufpll和OSERDES因为不在一个bank下导致无法进行mapping。见图1.

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)