使用XILINX公司的Spartan6芯片,也是最近半年的事情。该芯片由于上市时间不长,在使用该芯片的时候各位网友分享的心得也比较少;再加上第一次开发使用它,开发过程肯定会遇到很多很多棘手头疼的问题。可以说Spartan6芯片的使用者对它是又爱又恨呐!

1.Spartan6芯片的时钟资源,种类比较多,而且使用它的游戏规则也有不少变化。XILINX公司关于Spartan6芯片提供了一篇文档Xilinx UG382 Spartan-6 FPGA Clocking Resources User Guide ,里面有详细的说明和解析。

本文就是对该文进行浓缩,将几个关键问题用图表的方式重新解释一番。

1.弄清楚目前Spartan6提供哪些时钟资源和时钟BUFFER资源。

2.弄清楚各种时钟BUFFER的输入输出情况。这是最重要的,因为这些资源对信号从哪里来,到哪里去,给哪些对象使用是有硬性要求的。

下面一段是XILINX提供的关于各种时钟BUFFER使用规则。一定要把这几句话弄懂。原因首先是,它提供了时钟BUFFER的类型;其次,它定义各种时钟BUFFER的输入输出。

Understand the use of each clock buffer type and how they can work best for your design

1. BUFG/BUFGMUX – Global Clock; Clock of Fabric; legal support for IDDR2、ODDR2 clocking。

2. BUFH – Increases number or global clock rouTIng resources; CMT outputs if BUFG’s not used。

3. BUFIO2 – High speed clocking of IOSERDES/IOLOGIC (without DCM/PLL); Dedicated rouTIng to DCM/PLL/BUFG。

4. BUFPLL – SDR clocking of ISERDES2/OSERDES2。

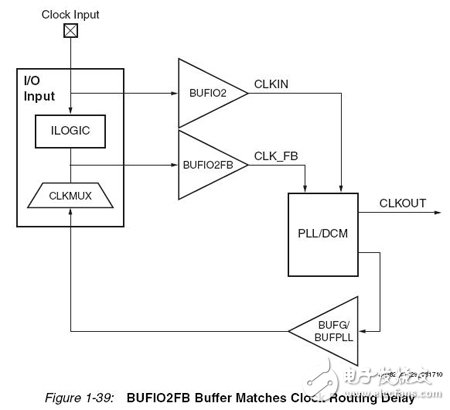

5. BUFIO2FB – Dedicated rouTIng for feedback for DCM/PLL; GTP and PLL are

also used to route through the BUFIO2FB。

说实话,我第一次阅读这段文字,还是摸不着门路,没有完全搞清楚。读完以后对芯片内的时钟资源布局无法建立一个清晰的图景。没关系,配合下面几个图,就会容易理解一些。

下面的图,如果对Spartan6相关的资料阅读广泛的话,下面的几幅图应是比较熟悉的啦。但这些图包含的信息量很大,值得拿出来给大家解惑。这些图可以很好的告诉使用者,时钟BUFFER的输入从哪里来,输出到哪里去!!!!

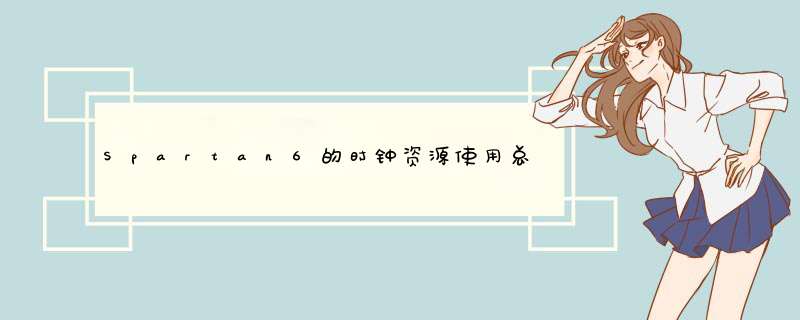

图1 BUFPLL和BUFIO2的图示

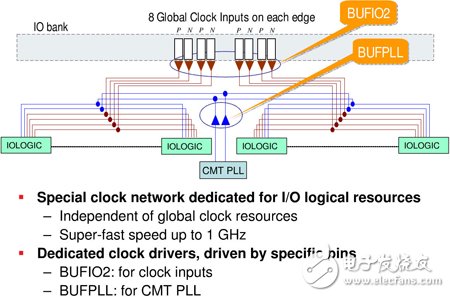

图2 BUFIO2的详细图示

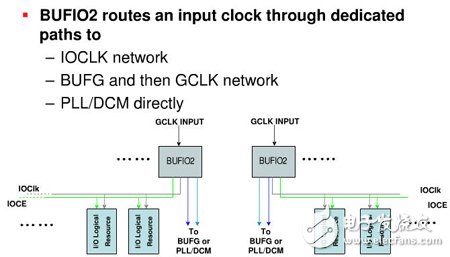

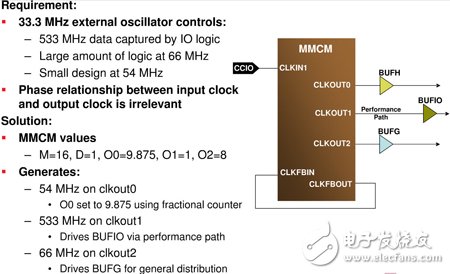

图2 CMT的输入输出详细图示

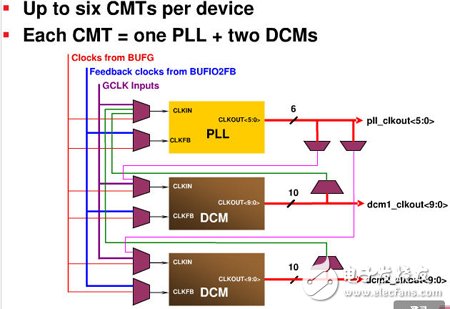

图3 一个CMT的使用案例举例

如果将上面的内容阅读完了后,看一下图4,如果你能彻底搞清楚他们的关系,那就说明对时钟资源已经建立清晰的图景了。

图4 Spartan6内部时钟资源关联图。

举个我开发过程中遇到的一个问题:

我的设计中,其中的某一个BANK,有系统的全局时钟输入信号,同时也有高速DDR输入信号。由于该DDR输入信号同时还需要一个随路时钟输入,它与全局时钟输入信号处于同一个BANK中。我的设计将该随路时钟信号通过一个例化的BUFIO2进行端接后,供设计代码使用作为DDR模块的时钟信号。

MAP阶段出现了问题,出现了ERROR报告,报告称我例化的BUFIO2不能place!!!!

不知道原因啊一开始,接下来就是痛苦的调试中。。。(几个通宵)

后来看了Xilinx UG382中下面一段话,才知道怎么解决。

The BUFIO2FB buffer matches the clock rouTIng delay between a CMT (PLL or DCM) reference input CLKIN and feedback CLKFB when used as shown in Figure 1-39. The ISE Design Suite automatically inserts matching BUFIO2FB and BUFIO2 buffers when the CMT feedback path is used。

呵呵。。。知道了我写该博文的原因了吧,对Spartan6的时钟资源一定要弄清楚!!!

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)