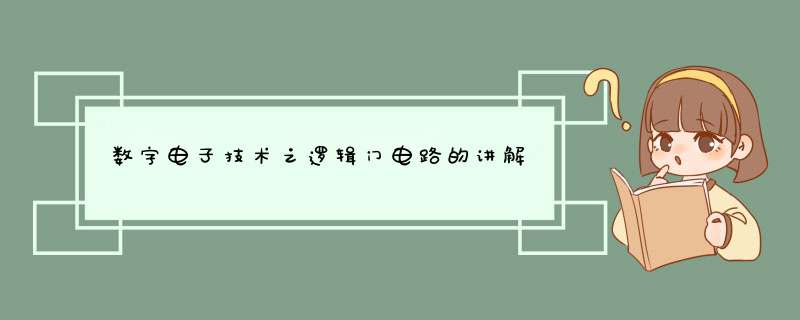

数字电路设计中逻辑门是最基本的运算单元,其中与门、或门和非门是最基本的逻辑门单元,但实际设计中用到的逻辑往往比与、或、非复杂得多,不过它们都可以利用与、或、非门组合实现。比如与非门、或非门、异或门和同或门等等。这些逻辑门的图形符号如下图:

如何利用门单元搭建电路?

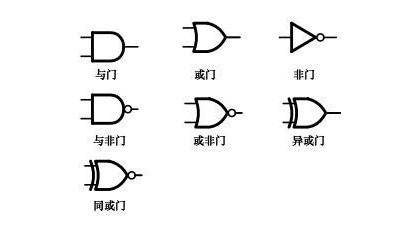

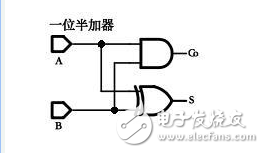

利用门单元搭建的电路称为门电路,按照一定的逻辑关系使不同的门单元连接起来实现我们所需要的逻辑功能,这就是数字电路设计的目的。下面给大家介绍两个利用逻辑门单元搭建一位半加器和一位全加器门电路的例子:

上图是由一个与门和一个异或门搭建的半加器电路,其中A和B是半加器的输入信号,S是半加器的结果输出,C是半加器的进位输出。

上图是由逻辑门单元搭建出来的一位全加器电路,A、B是全加器的输入端信号,Ci是全加器的进位输入信号,S是全加器结果输出,Co是全加器的进位输出。

为什么可以实现加法功能?下面简单分析一下上面两个门电路实现加法功能的原理,首先解释一下半加器和全加器的区别:半加器是只对输入信号A、B进行相加,不考虑进位;而全加器除了考虑A、B相加外还加上进位Ci。

其中,半加器相加,只有当A和B同时为1时,相加才会产生进位,因此Co=A&B。当A和B同时为0时,相加结果S=0。只有A和B其中一个为0另一个为1时,相加结果S=1,因此S=A^B。

全加器的运算复杂一点,当A、B、Ci三个输入其中有1个或者3个都为1时,相加结果S=1,否则S=0,因此S=A^B^Ci;当A、B、Ci三个输入中任意两个或者三个都为1时,相加就会产生进位Co=1,否则Co=0,因此Co=A&B|A&C|B&C。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)