对于数字电路来说,目前绝大部分的场合都是采用同步逻辑电路,而同步逻辑电路中必不可少的就是时钟。数字信号的可靠传输依赖于准确的时钟采样,一般情况下发送端和接收端都需要使用相同频率的工作时钟才可以保证数据不会丢失(有些特殊的应用中收发端可以采用大致相同频率工作时钟,但需要在数据格式或协议层面做些特殊处理)。为了把发送端的时钟信息传递到接收端以进行正确的信号采样,数字总线采用的时钟分配方式大体上可以分为3类,各有各的应用领域。

并行时钟

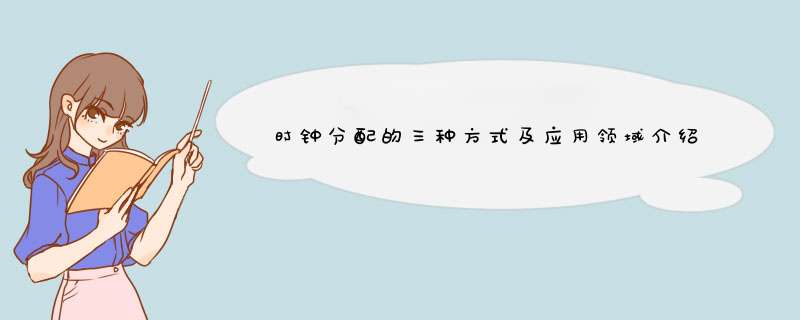

传统的并行总线使用一路时钟和多路信号线进行数据传输,如PCI总线、大部分CPU、DSP的本地总线等。这些总线工作时有一个系统时钟,数据的发出和接收都是在时钟的有效沿进行。下图是个采用并行时钟的总线例子。

为了保证接收端在时钟有效沿时采集到正确的数据,通常都有建立/保持时间的要求,以避免采到数据线上跳变时不稳定的状态,因此这种总线对于时钟和数据线间走线长度的差异都有严格要求。这种并行总线在使用中最大的挑战是当总线时钟速率超过几百MHz后就很难再提高了,因为其很多根并行线很难满足此时苛刻的走线等长的要求,特别是当总线上同时挂有多个设备时。

嵌入式时钟

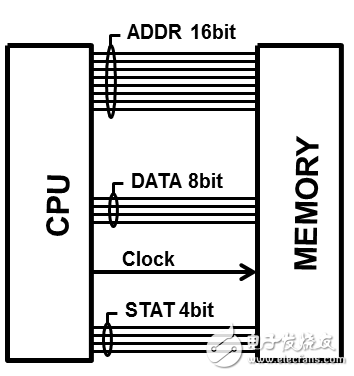

为了解决并行总线工作时钟频率很难提高的这个问题,一些系统和芯片的设计厂商提出了嵌入式时钟的概念。其思路首先是把原来很多根的并行线用一对或多对高速差分线来代替,节省了布线空间;然后把系统的时钟信息通过数据编码的方式嵌在数据流里,省去了专门的时钟走线。信号到了接收端,接收端采用相应的CDR(clock-data recovery)电路把数据流中内嵌的时钟信息提取出来再对数据采样。下图是个采用嵌入式时钟的总线例子。

这种方法由于不需要单独的时钟走线,各对差分线可以采用各自独立的CDR电路,所以对各对线的等长要求不太严格(即使要求严格也很容易实现,因为走线数量大大减少,而且信号都是点对点传输)。为了把时钟信息嵌在数据流里,需要对数据进行编码,比较常用的编码方式如ANSI的8b/10b编码,64b/66b编码、曼彻斯特编码以及对数据进行加扰等。目前流行的PCI-E、SATA、FC、XAUI、DP等都是采用的ANSI 的8b/10b编码。

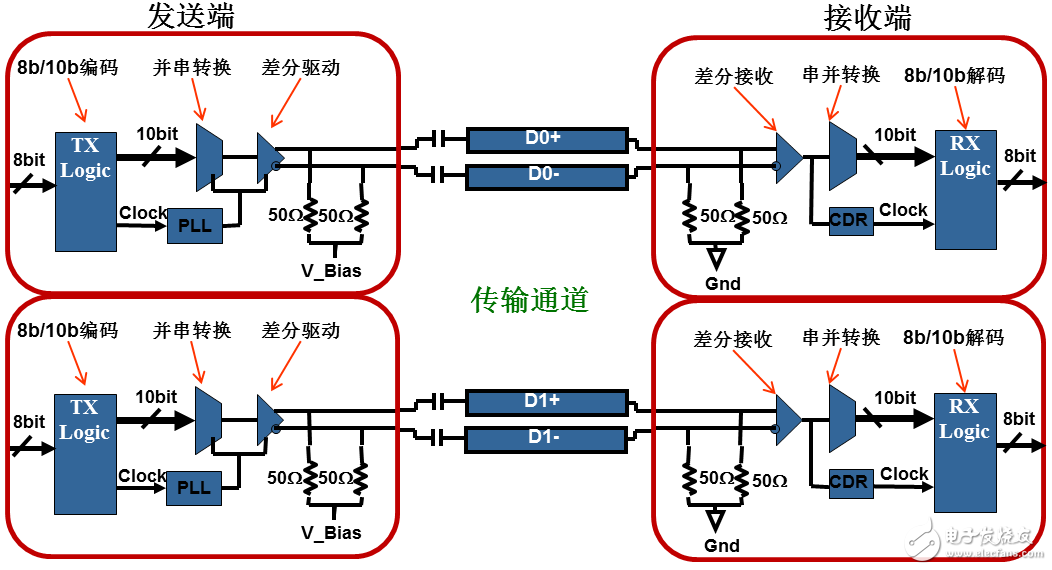

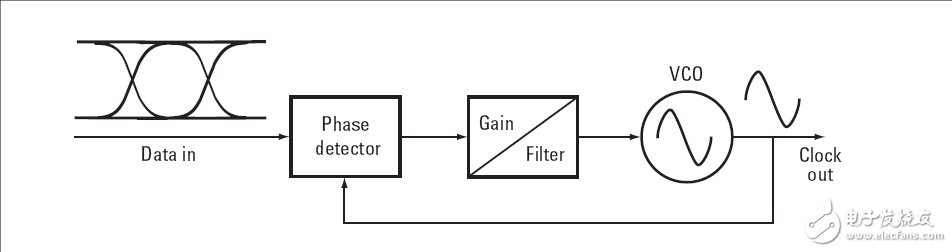

嵌入式时钟结构的关键在于CDR电路,CDR的工作原理如下图所示。CDR通常是用一个PLL电路实现,可以从数据中提取时钟。PLL电路通过鉴相器(Phase Detector)比较输入信号和本地VCO(压控振荡器)间的相差,并把相差信息通过环路滤波器(Filter)滤波后转换成低频的对VCO的控制电压信号,通过不断的比较和调整最终实现本地VCO对输入信号的时钟锁定。

采用这种时钟恢复方式后,由于CDR能跟踪上数据中的一部分低频抖动,所以数据传输中增加的低频抖动对于接收端采样影响不大,因此更适于长距离传输。(不过由于受到环路滤波器带宽的限制,数据线上的高频抖动仍然会对接收端采样产生比较大的影响。)

采用嵌入式时钟的缺点在于电路的复杂度增加,而且由于数据编码需要一些额外开销,降低了总线效率。

前向时钟

随着技术的发展,一些对总线吞吐速率和效率要求更高的应用中开始采用另一种时钟分配方式,即前向时钟(Forward Clocking)。前向时钟的实现得益于DLL (delay locked loop)电路的成熟。DLL电路最大的好处是可以很方便地用成熟的CMOS工艺大量集成,而且不会增加抖动。目前很多FPGA芯片如Xilinx公司Spartan/Virtex系列和Altera公司的StraTIx系列FPGA内部都集成了大量的DLL电路。

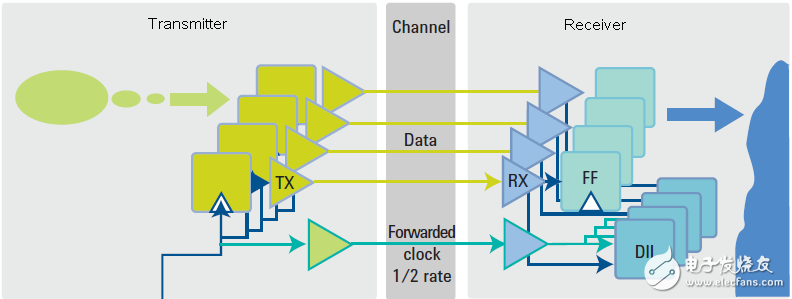

下图是一个前向时钟的典型应用:总线仍然有单独的时钟传输通路,而与传统并行总线所不同的是接收端每条信号路径上都有一个DLL电路。电路开始工作时可以有一个训练的过程,接收端的DLL在训练过程中可以根据每条链路的时延情况调整时延,从而保证每条数据线都有充分的建立保持时间。

采用前向时钟的总线因为有专门的时钟通路,不需要再对数据进行编解码,所以总线效率一般都比较高。还有一个好处是线路噪声和jitter对于时钟和数据线的影响基本是一样的(因为走线通常都在一起),所以对系统的影响可以消除到最小。

嵌入式时钟的电路对于线路上的高频抖动非常敏感,而采用前向时钟的电路对高频抖动的敏感度就相对小得多。前向时钟总线典型的数据速率在500Mbps~8Gbps。

在前向时钟的拓扑总线中,时钟速率通常是数据速率的一半(也有采用1/4速率、1/10或其它速率的),数据在上下边沿都采样,也就是通常所说的DDR方式。使用DDR采样的好处是时钟线和数据线在设计上需要的带宽是一样的,任何设计上的局限性(比如trace的衰减特性)对于时钟和数据线的影响是一样的。

前向时钟在一些关注效率、实时性,同时需要高吞吐量的总线上应用比较广泛,比如服务器上曾经应用的FB-DIMM内存总线、Intel公司CPU互连的QPI总线、AMD公司CPU的HT总线,还有象DDR/GDDR等总线也是使用相同的概念。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)