服务器分为很多种不同的类型:从机架式、刀片式和塔式到用于高密度计算的模块化配置类型。理想情况下,每台服务器应经过针对性优化来执行特定任务。然而,如果仔细观察的话可以发现大多数服务器设计都具备许多共同的特征。通常,它们具备多个处理器和热插拔存储器,各种通过PCIe连接到CPU和PCH的外围设备以及安全服务和电源管理解决方案,这里仅仅列出了几个常见的共同特征。尽管设计工程师为各种应用创建不同的解决方案,但在大多数情况下,其实是在对基本的服务器架构进行定制。

本文讨论了在旧式服务器设计中实现功能 #1的传统方法,并将其与现代服务器设计方法进行比较,后者使用PLD集成这些功能。此外,本文还讨论了使用其他集成可编程器件实现服务器中其他常用功能以降低复杂性和成本。

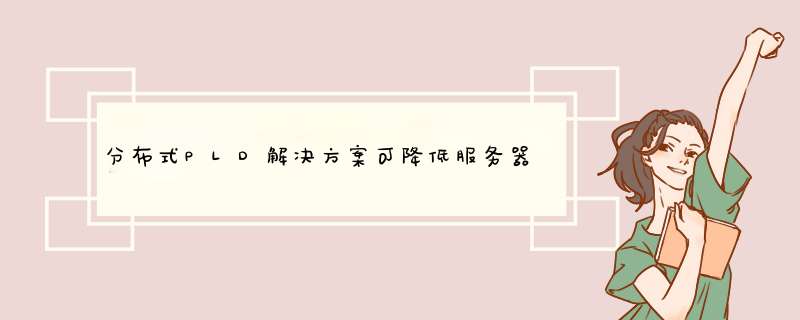

图1:8个PLD功能说明的服务器设计框图(设计实例)

功能 #1 - 电源管理、控制和胶合逻辑功能以前,设计工程师通常使用多种不同的分立元件来实现电源管理、控制和其他胶合逻辑功能。多年来这一直都是颇具成本效益的方法。但随着服务器设计日益复杂、功能越来越多,这类设计需要的器件也变得越来越多。现在,如果设计工程师要为多种类型的服务器设计功能 #1,采用离散元件将需要很多时间和人力。举个例子,电路板上复杂SoC器件的数量发生变化的话,电源数量、胶合逻辑以及其他控制功能的数量也要相应地发生变化。这就很可能要更改逻辑和基本时序。

因此,使用分立器件的解决方案不仅会拖累新款服务器硬件产品的上市进程,还会随着所需元件数量的增加而导致成本上升。此外,更改设计有时需要重新改整个电路板,不仅进一步拖延了项目进程,还增加了成本。

现代服务器系统通常将功能 #1集成到非易失性PLD中。PLD将在电路板上电之后立即开始工作(瞬时启动)。通常,实现功能 #1所需的逻辑资源和I/O数量取决于服务器类型。因此,能够提供丰富的I/O和逻辑资源选择的PLD器件非常适合实现功能 #1。

莱迪思MachXO3 FPGA系列以及上一代MachXO2系列(简称MachXO2/3)都能提供所需的功能。MachXO2/3器件是支持瞬时启动的非易失性PLD,提供640 LUT到9400 LUT以及22个I/O到384个I/O的器件选择。这些PLD可以在系统中透明地进行更新,并提供双引导支持以便从任何系统更新错误中恢复。这些器件只需一个3.3V电源即可工作,当该电源电压高于2.2V时,服务器主板电源管理算法即开始工作。因此,MachXO2/XO3是电路板上第一个启动,最后一个关闭的器件。这些器件支持多个I/O Bank,可以单独上电或断电而不影响其他模块的运行。这方面的优势使得它们能够集成多种异构功能,例如多个电源区块控制、带外信号发送和电源待机控制。凭借上述器件,设计工程师还能够将SPI、I2C和定时器/计数器接口添加到传统设计中,并支持多次可编程片上配置闪存。这些先进的器件提供5mm×5mm的QFN和BGA封装以及1mm和0.80mm的引脚间距选择。

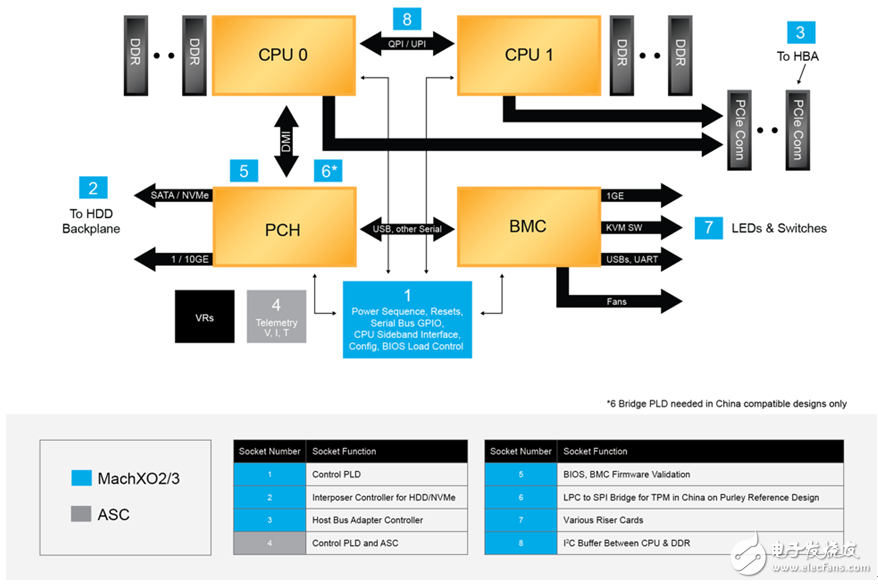

功能 #1集成到控制PLD(MachXO2/3)中

在图2中,MachXO2/3器件用于实现控制PLD功能,如电源/复位时序、各种类型的串行总线(I2C、SPI、eSPI、SGPIO等)、调试端口、LED驱动器、风扇PWM驱动器、前板开关传感以及其他一般GPIO功能。MachXO2/3器件支持1V信号,可实现带外信号功能集成,无需外部GTL收发器。当芯片运行时,设计工程师可使用莱迪思软件包中的Reveal工具调试控制PLD电路。该工具在PC上运行,可用作监视和捕获各种状态的逻辑分析器以追溯故障事件。例如,使用Reveal调试工具,设计工程师能够捕获许多导致故障状态的事件信息(包括寄存器、节点和引脚状态),并将其显示在PC显示器上。这可以显著减少系统电路板的调试用时。

图2:基于MachXO2/MachXO3的控制PLD

无中断更新I/O

控制PLD能够帮助设计工程师显着加速产品上市进程,在有限时间内满足市场对于全新定制硬件的需求的压力。有时候,在实现控制功能时会出现bug或系统整体结构需要的新功能。这时,对设计进行修改的一种常用方法是通过在系统更新、系统电源重新上电、载入经过重新编程的镜像来实现。这种方法需要进行电源复位,会中断整个服务器硬件的运行,降低可用性。为了确保高可用系统的连续运行,MachXO3器件可以保持I/O状态不变,同时刷新配置并初始化新配置。该功能称为无中断更新I/O。

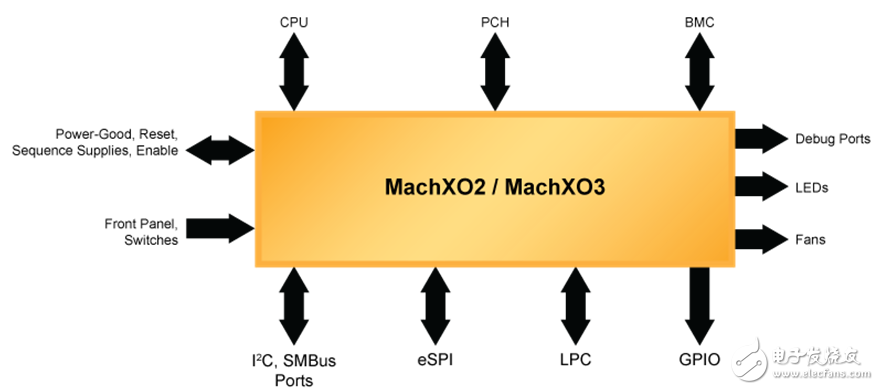

图3:无中断更新I/O是如何工作的

无中断更新I/O如何工作(图3)

为了实现零停机更新,MachXO2/MachXO3器件通过“后台更新”将新的配置数据加载到配置闪存中。一旦加载完毕,“TransFR”指令将新的PLD镜像文件从配置闪存传输到PLD的配置SRAM。执行“TransFR”指令的同时触发了“保持当前状态”功能,确保所有的I/O值在传输过程中保持不变。最后,在“逻辑初始化”步骤,状态机将开始重新启动电源管理并复位电源分配。这将导致电源关断,迫使电路板开始电源上电过程。

当新镜像创建的状态机进行初始化时,系统是如何保持用于控制电源以及其他逻辑信号的输出不变的?为了使得关键I/O在初始化过程中保持原状,莱迪思为每个关键的I/O添加了一个锁存MUX。它在状态机初始化过程中将输出保持为最后的已知状态,并在初始化过程完成之后将输出控制交还给状态机。该电路能够使用“Hitless_IO_Enable”输入区分正常(上电)启动和重新配置,可避免在正常的上电过程中发生关键输出I/O值被锁死的情况。

这种新功能的优势是显而易见的。它让制造商实现即时的配置更改成为可能,可马上纠正设计缺陷或向产品添加新功能。它在产品开发过程中也能发挥重要作用,让设计工程师能够在服务器安装过程中快速调试产品或在调试过程中更改特定的产品参数。

PLD的便利性和成本优势使其成为实现在系统设计更新、电源管理、监控和控制关键信号以及基本内务管理功能的理想选择。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)