DS1302是时钟,它的频率就是它的计时频率,32.768k是2的15次方,是秒的标准脉冲,按照DS1302的折算可以转换成精确的时间,进行秒分时日月年的计时,而瓷片电容的作用是在其有误差时进行调整误差,对一般使用者是用不到的,所以不接也行。

时钟芯片DS1302可靠起振的方法

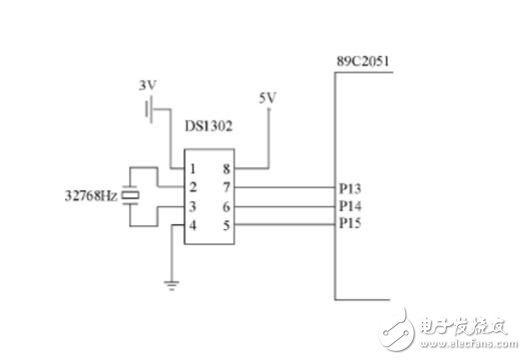

在实际使用中,我们发现DS1302的工作情况不够稳定,主要表现在实时时间的传送有时会出现误差,有时甚至整个芯片停止工作。我们对DS1302的工作电路进行了分析,其与单片机系统的连接如图2所示。

从图中可以看出,DS1302的外部电路十分简单,惟一外接的元件是32768Hz的晶振。通过实验我们发现:当外接晶振电路振荡时,DS1302计时正确;当外接晶振电路停振时,DS1302计时停止。因此,我们认为32768Hz晶振是造成DS1302工作不稳定的主要原因。

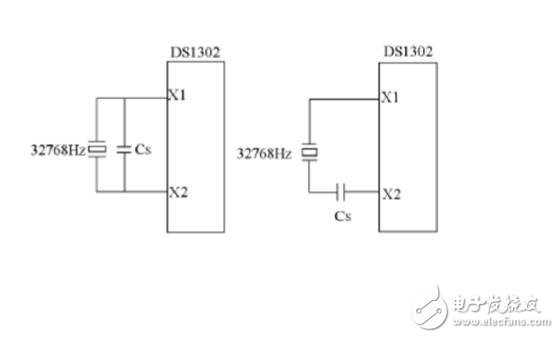

DS1302时钟的产生基于外接的晶体振荡器,振荡器的频率为32768Hz。该晶振通过引脚X1、X2直接连接至DS1302,即DS1302是依靠外部晶振与其内部的电容配合来产生时钟脉冲的。由于DS1302在芯片本身已经集成了6pF的电容,所以,为了获得稳定可靠的时钟,必须选用具有6pF负载电容的晶振。

然而,许多人在选用晶振时仅仅注意了晶振的额定频率值,而忽视了晶振的负载电容大小,甚至连许多经销商也不能提供所售晶振的负载电容。所以即使在使用中选用了符合32768Hz的晶振,但如果该晶振的负载电容与DS1302提供的6pF不一致时,就会影响晶振的起振或导致振荡频率的偏移,出现上述在应用中的问题。

当所选的晶振负载电容不是6pF时,可以采用增加辅助电容的方法提高或降低DS1302振荡器的电容性负载,使之与晶体所需的电容值匹配。如果已知晶体的负载电容为CI,若CI《6pF,则可以增加一个并联电容CS以产生所需的总负载电容CI,即CI=6pF+CS;若CI》6pF,则可以在晶体的一端增加一个串联电容CS,以产生所需的负载电容CI,即1/CI=1/6pF+1/CS,通过计算即可得出应增加的辅助电容大小。

在使用前对晶体的负载电容并不知道的情况下,通过测定晶体振荡频率的方法可以确定该晶体的负载电容。对于晶体振荡器来说,其振荡频率与负载电容之间的关系是确定的。以本文讨论的DS1302使用的32768Hz晶振为例:当它工作于所要求的负载电容时,能较准确地产生32768Hz的频率;当它的负载电容小于6pF时,其振荡频率会正向偏移。

当它的负载电容大于6pF时,其振荡频率就会负向偏移。因此,对于未知负载电容的晶体应首先采用实验的方法,在其两端加入辅助电容使晶体起振,然后用频率计测出振荡频率。若测得频率大于32768Hz,说明负载电容偏小;若测得频率小于32768Hz,说明负载电容偏大。

对辅助电容逐步调整,最终使振荡频率尽可能接近32768Hz,则此时晶体端所接负载电容的总和就是适合该晶体的负载电容。结论以上方法经我们在实际工作中多次使用,证明确实有效。它放宽了DS1302在使用中对晶振的条件要求,增强了DS1302在工作中的稳定性,对DS1302更广泛地应用具有积极的意义。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)