基于双DSP的并联控制系统中串行通信的研究

摘 要:概要地介绍了TMS320F2812 DSP 的基本性能,重点介绍了利用DSP 的SPI 模块进行双DSP 同步串行通信,以及在Visual Basic 6.0 下,利用MSComm 控件实现上位PC 机和下位DSP 之间异步串行通信的具体实现方式。最后给出了一个采用RS-232 串行通信标准实现信息传输的实例。串行通信简单,界面友好,应用领域广泛。

引言

随着数字信号处理器(DSP)在系统控制领域中的广泛应用,控制各系统的DSP 之间 通信问题也越来越突出。利用DSP 本身的高速同步串行接口(SPI)模块,可以让DSP 直 接对接实现芯片间的同步串行通信。有时为了充分利用PC 机资源,让一些在智能仪器上难以解决的问题诸如曲线显示等可以在PC 机上得以实现,这就需要DSP 内嵌的串行通信接口 (SCI)模块,实现DSP 与上位机的异步串行通讯。

本文所介绍的通信方法的背景是为课题组搭建双开关磁阻伺服电动机并联传动系统 (SRSD),系统使用的是TMS320F2812 芯片,具有SPI 模块和SCI 模块[1]。本文详细介绍 了SPI 模块和SCI 模块各自进行串行通信的硬件连接和软件实现方法,从而完成了基于 TMS320F2812 的双SRSD 系统通信模块的实现。

1 系统简介

双电机并联系统有很多优点,它比单电机系统在处理电机空间放置方式上更为灵活,并且有利于改进电机的特性。相对于单电机系统,在相同的输出情况下,双电机的总转动惯量更小,从而可以减少运行时的电能消耗。此外,当双电机中的一台损坏后,另一台仍可以在短时间内或适当减少负载的情况下继续运行,提高了系统的可靠性[3]。

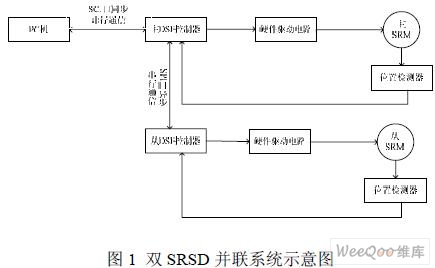

本文背景以SRSD 为主要研究对象,以位置输出为主要控制量。在单机系统的基础上, 经过改进,设计出双SRSD 并联系统,系统框图如图1 所示。

2 串行通信原理及特性

在计算机中,通常用8 位的二进制代码来表示一个字符,一条信息的各位字符的二进制代码被按由低到高位的顺序,依次地发送出去的通信方式叫做串行通信。它的特点是按位发送。根据信息的传送方向,串行通信可以分为单工通信、半双工通信和全双工通信。在本文中采用的是全双工的通信方式。串行通信按照传输方式的不同又可以分为同步方式和异步方 式。同步方式较复杂,但传送速率比异步方式高。本文中SPI 采用是同步方式,SCI 采用是 异步方式。

TMS320F2812 的SPI 是一个高速的同步串行输入/输出端口,一般用来实现DSP 控制器 之间和DSP 与外围设备之间的通信。SPI 有两种 *** 作模式:主 *** 作模式和从 *** 作模式。主片 控制了时钟信号(SPICLK),它可以在任何时候通过发送SPICLK 信号来启动数据传输。无论是主片还是从片,数据都是在SPICLK 的某个边沿移出移位寄存器,在SPICLK 相反的边沿锁存在移位寄存器中,并且输出和接受数据都是同时进行的。

芯片的 SCI 是一个双线通信的异步串行通信接口,也称UART 口,一般用于接上位机(以下简称PC 机)。

3 同步通信模块的设计

3.1 基于SPI 模块的硬件设计

让两个 DSP 分别工作在主、从 *** 作模式下,两者的引脚连接如图2 所示。主处理器通 过SPICLK 脚向整个通信网提供串行时钟,控制着系统的数据传输;通过SPISTE 脚给从处 理器提供片选信号,低电平有效;通过SPISIMO 脚把数据输出到从处理器的SPISIMO 脚上; 通过SPISOMI 脚接受从机处理器SPISOMI 脚上的数据。

3.2 同步通信流程设计及软件实现

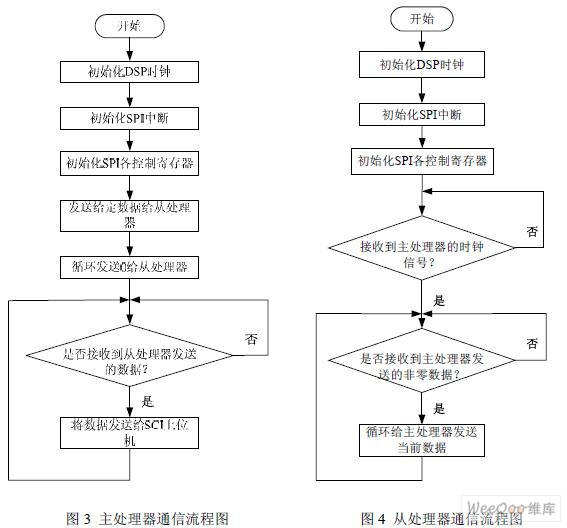

在设计时,主处理器先向从处理器发送给定信息,发送完毕后,循环发送0,使SPICLK 不停地有时钟脉冲输出,并等待接受从处理器发送的数据。从处理器先是等待给定信息,如果接收到非零数据,则进行下一步运行并不断向主处理器发送当前数据。

SPI 通信主处理器的流程图和从处理器的流程图分别如图3、图4 所示。

在完成两个DSP 时钟和中断初始化后,分别对其SPI 寄存器进行设置,让其分别处于 master 和slave 模式。主、从处理器都采用查询方式发送数据,中断方式接受数据。

查询方式发送是判断SPI 发送缓冲器已满标志位(SPISTS.bit.BUFFULL_FLAG)是否为空,如果为空,则将数据写入发送缓冲寄存器(SPITXBUF)中,启动SPISIMO 引脚的数据发送,数据发送完毕后SPISTS.bit.BUFFULL_FLAG 自动清零,等待下一次发送。

中断方式接受是在SPI 中断使能位(SPICTL.bit.SPIINTENA)置位的情况下,如果接收 到数据传送到SPI 串行数据寄存器(SPIDAT)中,SPI 中断标志位(SPISTS.bit.INT_FLAG)置位且触发中断,并将数据转移到接受缓冲寄存器(SPIRXBUF)中,如果SPIRXBUF 中数据被读取,则SPISTS.bit.INT_FLAG 自动清零,等待下一次接受中断。

SPI 部分发送和接受程序如下:

void spi_TxProcess()

{

while(SpiRegs.SPISTS.bit.BUFFULL_FLAG==1) {}

/*判断SPISTS.bit.BUFFULL_FLAG)是否为空*/

if(SpiRegs.SPISTS.bit.BUFFULL_FLAG==0)

{

SpiRegs.SPITXBUF=slave_value;

/*向SPITXBUF 写入数据以启动数据发送*/

}

}

interrupt void SPIRXINTA_ISR(void)

/*中断方式接受*/

{

TX_data2=SpiRegs.SPIRXBUF;

/*读取SpiRegs.SPIRXBUF 后自动清除中断标志位*/

return;

}

4 异步通信模块的设计

4.1 基于SCI 的硬件设计

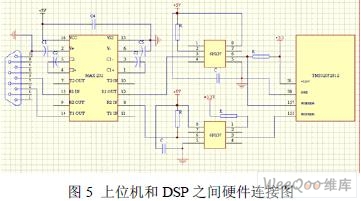

图 5 为上位机和DSP 的硬件连接图。RS-232C 标准采用负逻辑:逻辑“1”为-5V~-15V 之间的低电平,通常用-12V 表示;逻辑“0”为+5V~+15V 之间的高电平,通常用+12V 表示。 上述标准称为EIA 电平。

RS-232C 是用正负电压来表示逻辑状态,并且是负逻辑,而TTL 则以高低TTL 器件电平表示逻辑状态,且为正逻辑,两者的规定是不同的。为了能够将与EIA 器件连接,保证二者之间正常通信,必须在它们之间进行电平和逻辑关系的变换。本Maxim 公司生产的集 成芯片MAX232 来实现这一变换[4]。变化后的电平在经过6N137 转换为适合TMS320F2812 的电平在+3.3V 以内的信号。

4.2 SCI 通信的软件实现

通信前,发送端和接受端必须使用双方协商一致的通信协议,数据被拆分成为(bit)进行传送。传送的顺序一次为起始位、数据位、奇偶校验位、停止位。每秒钟传送的bit 数由波特率来决定。本文中的通信协议设定为:波特率38400bit/s,8 位数据位,无奇偶校验,1 位停止位,数据传输同时采用ASCⅡ码和二进制两种形式。

上位机采用Visual Basic6.0(以下简称VB)语言编程实现,利用VB 中提供的MSComm 控件可以实现PC 机与下位机的通信。利用MSComm 实现通信有两种方法:一是事件驱动 方法,也就是OnComm 事件。当有数据到达端口或端口状态发生改变或有通信错误产生时, 都将发生OnComm 事件。另一种就是查询方式。查询方式是通过周期性读取缓冲区的信号来发现是否有事件发生并进行处理的方法。本设计中,发送采用查询方式,接受采用事件驱 动方法。MSComm 控件初始化程序如下:

MSComm1.CommPort = 1 '端口号'

MSComm1.SetTIngs = "38400,n,8,1"

'波特率38400bit/s,8 位数据位,无奇偶校验,1 位停止位'

MSComm1.InputLen = 0

MSComm1.InBufferCount = 0 '清空接收缓冲区'

MSComm1.OutBufferCount = 0 '清空'

MSComm1.RThreshold = 1 '接收缓冲区或发送缓冲区中可以接收的字符数'

MSComm1.PortOpen = True

应实际要求,我们要在通信中同时传输数据和控制字符,所以数据传输同时采用ASCⅡ 码和二进制两种形式。这就需要在每次传输前改变MSComm1.InputMode 的属性。

TMS320F2812(SPI 通信中主处理器)在完成时钟和中断初始化后,对其SCI 寄存器进 行设置,使其通信协议和上位机一致。TMS320F2812 采用查询方式给上位机发送数据,中 断方式接受上位机的数据。SCI 寄存器设置如下:

SciaRegs.SCICCR.all=0x0007;

/*一个停止位,禁止奇偶校验,禁止自测,8 个字符*/

SciaRegs.SCICTL1.all=0x0003;

/*禁止接受错误中断,复位,禁止休眠,开启发送使能*/

SciaRegs.SCICTL2.all=0x0002;

/*开接受中断,关发送中断*/

SciaRegs.SCIHBAUD=0x00;

SciaRegs.SCILBAUD=0x79;

/*波特率38400*/

SciaRegs.SCICTL1.all=0x0023;

/*开始使能SCIA*/

5 结束语

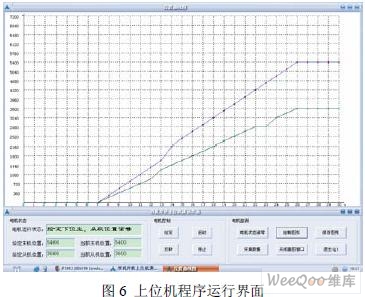

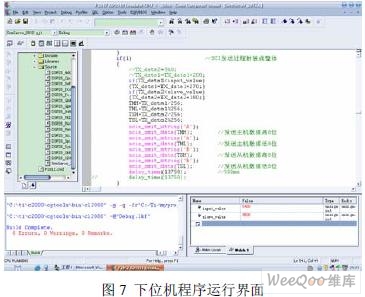

以上为解决两个DSP 之间以及DSP 与PC 机之间的通信的软硬件设计方案,当上位机 发送给定信息(位置信息)后,下位机接受到数据并传输给SPI 处理器,上位机和下位机界 面如图6、图7。

系统的最大特点是根据实际需要,采用同时同步和异步两通信方式。双系统间的同步串 行通信,保证了双系统运行的同步性;通过PC 机和上位机的异步串行通信,实现把DSP 采集的一系列数据通过串口发送至PC 机,解决了DSP 存储空间有限的问题,在PC 上可以很方便地对数据进行一些在DSP 上难以实现的处理,得到一些数据曲线等,效果直观便捷。此系统已应用与某一开关磁阻电机电机并联控制系统中,运行稳定,通信性能良好。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)